### ANALYSIS AND SUPPRESSION ON SIMULTANEOUS SWITCHING NOISE COUPLING BETWEEN MULTI-CAVITIES FOR MULTILAYER PCBS

## C.-S. Chang and M.-P. Houng

Institute of Microelectronics Department of Electrical Engineering National Cheng-Kung University No. 1 University Road, Tainan City 701, Taiwan, R.O.C.

### D.-B. Lin, K.-C. Hung, and R.-F. Hong

Institute of Computer and Communication EngineeringNational Taipei University of Technology1, Sec. 3, Chung-hsiao E. Road, Taipei, 10608, Taiwan, R.O.C.

**Abstract**—In this letter, an easy concept to eliminate the simultaneous switching noise (SSN) in multilayer board is proposed. By using low impedance element can provide a short path to lead noise to ground, called virtual shield. This method could effectively suppress the first mode of the parallel resonance, and the wider-band suppression could be obtained by array short via. It is also proved that the virtual shield concept needs to be placed as the excited source at the same layer.

## 1. INTRODUCTION

Simultaneous switching noise (SSN) in printed circuit boards (PCBs) or multi-chip module (MCM), commonly known as delta-I or ground bounce noise (GBN), has become major concerns of the high-speed digital circuit with low voltage levels and fast edge rates. The power and ground planes constitute the power-bus which is actually a parallel-plate structure. The resonance noise propagating in this structure causes the power integrity (PI) problems for the circuit.

Nowadays, high-integration and high-complexity circuit design makes different DC-level to provide the usage of relative circuits such as digital circuit and RF systems. In this way, many researches focus on the SSN problem in the single power and ground plane [1-5]. However, the noise coupling in the multilayer structures are also a serious issue in high-speed digital circuits. Slot is widely used in microwave components [6–8]. The slot is also taken to discriminate different DClevel in the multilayer power/ground planes [9–11]. Because of the rapid switching current, the switching noise appears in high-speed digital circuits. The SSN not only transmits in its own power and ground plane, but also couples to neighboring power/ground plane through slots [12]. Therefore, the power integrity of circuits is affected. In previous researches, the optimum position method [13] is making slot to suppress the noise instead of adding extra passive elements. This method applied for high level circuit design is inappropriate because the coupling theory accuracy is based on that: (a) slot is smaller relative to the electrical wavelength, (b) slot position should be taken away from the plane edge, and (c) source can not be too close to the slot. Other positions are still affected by resonance. It is hard to find null position in real situation.

This work proposed an approach which was considered that coupled- and slot-effect eliminate SSN in multilayer structure. This approach could cause the potential difference of the slot closing to zero, called "virtual shield". The effect of "virtual shield" could efficiently eliminate the SSN coupling to the adjacent cavity. The simple approach to reach zero potential difference is obtained by adding short via or decoupling capacitor.

### 2. STRUCTURE DESIGN

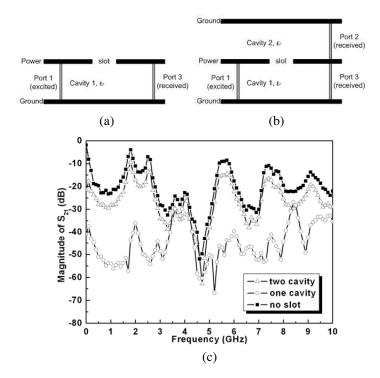

Nowadays, EMC design of power network distribution, slots are widely used to destroy the propagation path for isolating the switching noise transmission. This method is able to isolate noise efficiently in single power and ground plane as shown in Figure 1(a). Power plane with slot in multilayer power/ground plane circuits is shown in Figure 1(b). The switching noise couples through the slot in multilayer structure; and then the resonance mode will be produced which makes the noise couple back. In this way, the slot loses the designed goal for isolating the noise; we called it "cover effect" as shown in Figure 1(c). The switching noise couple back through slot due to the upper ground generates a cover effect. Because of the cover effect, the function of slot is failed, and results in considerable noise coupling. This effect is less investigated and discussed broadly in the past power integrity design. This work proposed a new concept that virtual shield was obtained by making the zero potential difference between the edges of slot. This approach could eliminate the noise coupling to nearly

cavities as shown in Figure 1.

**Figure 1.** The configuration of cavity with slot (a) one cavity, (b) two cavities, (c) compared the suppression results of one and two cavities with no slot configuration.

### 3. RESULTS AND DISCUSSION

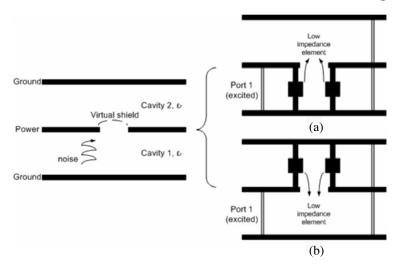

# 3.1. Short Via and Excited Source Placed at the Same Cavity

The short via was placed at the center of slot edges in the cavity 1 as shown in Figure 2 (a). Here, we do not consider the short phenomenon which is caused by short via between power and ground planes for demonstrating the feasibility of this approach. The dimension of the substrate is  $40 \text{ mm} \times 40 \text{ mm}$  and its thickness is 0.4 mm, and the dimension of the slot is  $10 \text{ mm} \times 1 \text{ mm}$ . The dielectric constant of the substrate is 4.4. The EM full wave Ansoft HFSS simulation tool is used to simulate the switching noise performance of the multilayer configuration. The location of the excitation port is at the cavity

Figure 2. The concept of virtual shield, (a) low impedance elements are placed at cavity 1, and (b) at cavity 2.

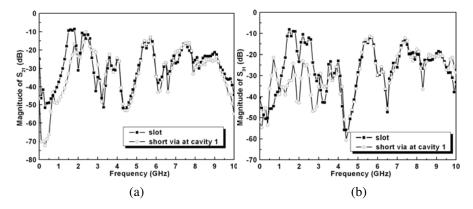

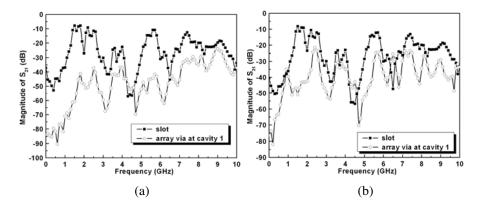

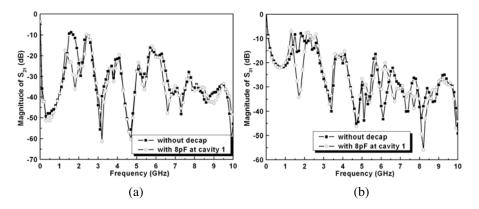

1 (port 1), and the receiving ports are at the cavity 2 (port 2) and cavity 1 (port 3), respectively. Compared with adding no short via in the cavity 1 and 2, it is seen that the short via eliminates with averagely  $10 \, dB$  for the first mode as shown in Figures 3(a)-(b). The results demonstrated that the short via could cause the zero-potentialdifference to reach virtual shield and eliminate the SSN in multilayer. To suppress the high-order modes could obtain wider suppressive bandwidth by utilizing array short via. Figure 4 shows the measured results for adding array short via. From the measured results shown in this figure, we can find that the SSN is suppressed from dc to 10 GHz with the bandwidth around 10 GHz, and the bandwidth is defined by the insertion loss lower than  $-20 \,\mathrm{dB}$ . It means that the slot with array short via efficiently suppresses the noise. In the following case, the low impedance was obtained by adding decoupling capacitor to reach the virtual shield. Figure 5 shows the measured results with decoupling capacitor of 8 pF, the corresponding parameters are as similar as Figure 2. It is seen that the first mode of switching noise was suppressed by resonance frequency of decoupling capacitor of 8 pF, and the broadband suppression also could be obtained by array decoupling capacitors.

171

Figure 3. The virtual shield was reached by short via in the case that short via and excited source at the same layer, (a) receiving port at cavity 2, and (b) at cavity 1.

Figure 4. The virtual shield was reached by array short via in the case that short via and excited source at the same layer, (a) receiving port at cavity 2, and (b) at cavity 1.

# **3.2.** Short Via and Excited Source Placed at the Different Layer

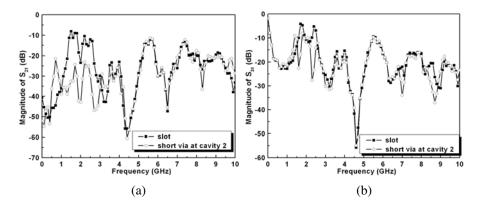

In this section, the short via was placed at the center of slot edges in the cavity 2 as shown in Figure 2(b). The eliminated result for receiving port located at the cavity 2 is shown in Figure 6(a), which shows that the switching noise is suppressed from 40 MHz to 5.2 GHz with the bandwidth around 4.16 GHz. The wider-band suppression also could be obtained by adding array short via. Figure 6(b) shows the measured

result of the SSN for the receiving port located at the cavity 1. When the frequency of S31 is between 1.8 GHz to 2.5 GHz, the switching noise at the cavity 1 was still worse after applying suppression method. The reason is that the short via forms a bridge which is connected with the edge of slot. The bridge provides additional propagation path to the port 3 and makes the noise feedback to the cavity 1. In this situation, the elimination behavior will be broken. Therefore, the proposed concept needs to be placed at the same layer as excited port to obtain the efficient switching noise suppression.

Figure 5. The virtual shield was reached by decoupling capacitor in the case that short via and excited source at the same layer, (a) receiving port at cavity 2, and (b) at cavity 1.

Figure 6. The virtual shield was reached by array short via in the case that short via and excited source at different layer, (a) receiving port at cavity 2, and (b) at cavity 1.

#### 4. CONCLUSION

In this work, the virtual shield is proposed to eliminate the switching noise in multilayer configuration. The wider-band SSN suppression could be obtained by the virtual shield with array short via. The proposed concept can suppress the SSN coupling to nearby cavity and does not destroy the structure of the slot. If the low impedance elements are placed at the layer without excited port, the short via will formed a bridge which is connected to the edge of slot. This bridge provides additional propagation path to the port 3 and causes the noise feedback to the cavity 1. In order to avoid the elimination behavior is broken, the virtual shield has to be placed at the same layer as excited port.

### ACKNOWLEDGMENT

The financial support of this study by the National Science Council of the Republic of China under Grant NSC 96-2221-E-006-353-MY2 is greatly appreciated.

#### REFERENCES

- Chen, R. L., C. Ji, T. H. Hubing, and S. Weimin, "Analytical model for the rectangular power-ground structure including radiation loss," *IEEE Transactions on Electromagnetic Compatibility*, Vol. 47, No. 1, 10–16, 2005.

- Chen, J., T. H. Hubing, T. P. V. Doren, and R. E. DuBroff, "Power bus isolation using power islands in printed circuit boards," *IEEE Transactions on Electromagnetic Compatibility*, Vol. 44, No. 2, 373–380, 2002.

- Wan, L., P. M. Raj, D. Balaraman, P. Muthana, S. K. Bhattacharya, M. Varadarajan, I. R. Abothu, M. Swaminathan, and R. Tummala, "Embedded decoupling capacitor performance in high speed circuits," *Electronic Components and Technology*, *IEEE ECTC Proceedings*, Vol. 2, 1617–1622, 2005.

- 4. Wu, T. L., S. T. Chen, J. N. Hwang, and Y. H. Lin, "Numerical and experimental investigation of radiation caused by the switching noise on the partitioned DC reference planes of high speed digital PCB," *IEEE Transactions on Electromagnetic Compatibility*, Vol. 46, No. 1, 33–45, 2004.

- 5. Chang, C. S., D. B. Lin, K. C. Hung, I. T. Tang, and M. P. Houng, "Simultaneous switching noise mitigation capability with low

parasitic effect using aperiodic high-impedance surface structure," *Progress In Electromagnetics Research Letters*, Vol. 4, 149–158, 2008.

- Wounchoum, P., D. Worasawate, C. Phongcharoenpanich, and M. Krairiksh, "A two-slot array antenna on a concentric sectoral cylindrical cavity excited by a coupling slot," *Progress In Electromagnetics Research*, PIER 86, 135–154, 2008.

- Sadat, S., M. Fardis, F. G. Gharakhili, and G. Dadashzadeh, "A compact microstrip square-ring slot antenna for UWB applications," *Progress In Electromagnetics Research*, PIER 67, 173–179, 2007.

- 8. Das, S., A. Chakrabarty, and A. Chakraborty, "Characteristics of an offset longitudinal/transverse slot coupled crossed waveguide junction using multiple cavity modeling technique considering the TE00 mode at the slot aperture, "*Progress In Electromagnetics Research*, PIER 67, 297–316, 2007.

- Lee, J., Y. M. Seng, M. K. Iyer, and J. Kim, "Investigation of plane-to-plane noise coupling through cutout in multi-layer power-ground planes," *IEEE Electronics Packaging Technology Conference*, 257–260, 2002.

- 10. Leone, M., "The radiation of a rectangular power-bus structure at multiple cavity-mode resonances," *IEEE Transactions on Electromagnetic Compatibility*, Vol. 45, 486–492, 2003.

- Wu, C. T., G. H. Shiue, S. M. Lin, and R. B. Wu, "Composite effects of reflections and ground bounce for signal line through a split power plane, "*IEEE Transactions on Advanced Packaging*, Vol. 25, No. 2, 297–301, 2002

- Antonini, G., A. C. Scogna, A. Orlandi, and V. Ricchiuti, "Cross-SSN analysis in multilayer printed circuit boards," *IEEE International Symposium on Electromagnetic Compatibility*, Vol. 3, 705–710, 2005.

- Lee, J., M. D. Rotaru, M. K. Iyer, H. Kim, and J. Kim, "Analysis and suppression of SSN noise coupling between power/ground plane cavities through cutouts in multilayer packages and PCBs," *IEEE Transactions on Advanced Packaging*, Vol. 28, 298–309, 2005.