# PARASITIC CAPACITANCE CANCELLATION OF INTEGRATED EMI FILTER USING SPLIT GROUND STRUCTURE

# H.-F. Huang and M. Ye\*

School of Electronic and Information Engineering, South China University of Technology, Guangzhou, China

**Abstract**—A convenient method for canceling the parasitic winding capacitance of integrated electromagnetic interference (EMI) filter is proposed. Based on the concept of split ground structure, mutual inductances and structural capacitances can be appropriately utilized to expand the effective frequency range in common mode (CM) noise suppression. Compared with the former approaches, it requires no additional conductor layers or components since the split winding can simultaneously serve for CM capacitance. To demonstrate the parasitic capacitance cancellation mechanism, a simplified equivalent circuit is derived and investigated. Besides, the design procedure with considered structural constraints is presented to obtain the best parasitic capacitance cancellation effect. Prototype of an integrated cm filter with split ground layers is designed and constructed. Experimental results show the split winding can effectively shift the resonance frequency of filter inductor, and hence better filtering characteristics can be achieved.

### 1. INTRODUCTION

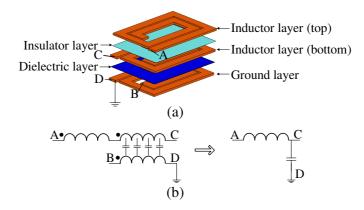

The EMI filters are widely used in practical power electronics systems for noise suppression [1]. In order to improve high frequency (HF) performance and reduce size and profile, the integrated EMI filters have been proposed based on advanced integration and packaging technologies [2,3]. As fundamental CM element, the integrated LC hybrid winding consists of a dielectric substrate with conductor windings directly deposited on both sides, thus resulting in a structure having both sufficient inductance and capacitance. As seen in

Received June 21 2012, Accepted 16 August 2012, Scheduled 22 August 2012

<sup>\*</sup> Corresponding author: Mao Ye (y.mao@mail.scut.edu.cn).

**Figure 1.** Original integrated LC hybrid winding. (a) Winding structure, (b) equivalent circuits.

Figure 1(a), by properly terminating the four terminals A, B, C, and D, its equivalent circuits as shown in Figure 1(b) indicated that the hybrid winding could be configured as low-pass filter. However, in order to get large enough CM inductance while maintaining a low-profile structure, the planar CM choke normally has multi-layer windings. As the conductor surface area of the planar structure is considerably increased compared to the wire-wound toroidal choke, its equivalent parallel capacitance (EPC) will be greatly increased if the windings are just simple stacked together. In general, the effective filter frequency range is limited since EPC may resonate with the CM inductance at very low frequencies [8, 9].

Several approaches have been proposed to reduce or cancel the EPC of filter inductors. Typically, for integrated form, a staggered and interleaving winding structure in [2–5] can effectively reduce the parasitic winding capacitance, but at the price of greatly increased winding complexity and thickness. A more feasible solution was proposed in [6,7], where an embedded conductive layer was inserted into the CM winding and grounded to realize the parasitic capacitance cancellation. Besides, the mutual capacitance or mutual inductance was utilized in [9–18] with the help of additional passive circuits.

The use of split ground structure to cancel parasitic capacitance of CM inductor is introduced in this paper. Specifically, the original ground winding is split into two parts with separate ground wires. These mutually coupled windings can then be used to achieve the EPC cancellation without negative effects upon the differential mode (DM) performance. As consequence, no extra conductor layers or components are needed in filter design.

The paper is organized as follows. Section 2 presents the equivalent circuit to demonstrate the parasitic capacitance cancellation mechanism. Section 3 follows with the design procedure of split winding. A graphical user interface (GUI) window is developed and implemented in Matlab to increase the labor efficiency. The improved integrated CM filter with split ground windings is then successfully designed and constructed. Experimental results confirm the effectiveness of proposed technology in Section 4. Finally, Section 5 concludes the paper.

# 2. PARASITIC CAPACITANCE CANCELLATION MECHANISM

Neglecting the losses, consider a practical planar inductor L with a certain value of parallel winding capacitance  $C_p$ . The equivalent impedance is given by:

$$Z = \frac{1}{Y} = \frac{1}{1/j\omega L + j\omega C_p} = \frac{j\omega L}{1 - \omega^2 L C_p}$$

(1)

The purpose of parasitic capacitance cancellation is to make Z become  $j\omega L$ , which is the impedance of an ideal inductor. According to (1), another LC resonance needs to be introduced to make item  $+\omega^2 L'C'$  added into the denominator with  $+\omega^2 L'C' = +\omega^2 LC_p$  satisfied [7].

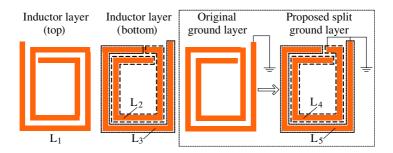

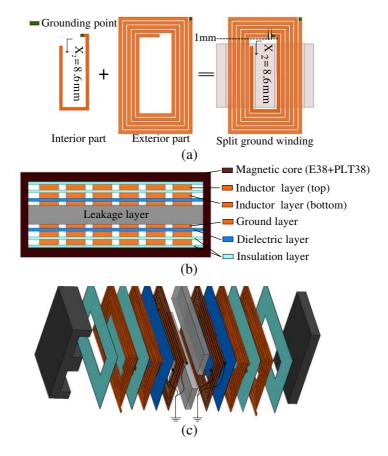

In order to realize this idea without the use of extra resources, a split winding with two separated parts (including exterior and interior) is applied in integrated EMI filter design to replace the original complete ground layer, as shown in Figure 2. From its physical structure, the lumped equivalent circuit shown in Figure 3 can be derived, where the interior and exterior parts of split winding are represented by  $L_4$  and  $L_5$ , respectively.  $L_2$  and  $L_3$  represent the

Figure 2. Proposed split ground winding.

Figure 3. Equivalent circuit with split ground winding.

Figure 4. Decoupled circuits. (a) First stage decoupled circuit, (b) final decoupled circuit.

winding parts of inductor layer (bottom) which are directly across from  $L_4$  and  $L_5$ . It can be obviously noticed that inductance of the two winding pairs are identical ( $L_2 = L_4$  and  $L_3 = L_5$ ). Additionally,  $L_1$  is the remaining winding part of CM inductor layers except  $L_2$  and  $L_3$ . The distributed capacitances  $C_1$  and  $C_2$  are generated with dielectric layer between inductor winding (bottom) and two split ground winding parts and their effects are represented by shunt capacitors located at both sides.

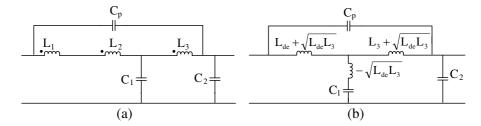

It is easy for the planar structure to get high coupling coefficient. To simplify the decoupling analysis, all mutual couplings as depicted in Figure 3 are assumed to be ideal. The decoupled circuits of Figure 3 can then be seen in Figure 4, where mutual inductance  $-\sqrt{L_{de}L_3}$  and distributed capacitance  $C_1$  are utilized to generated the resonance for achieving parasitic capacitance cancellation and  $L_{de} = (\sqrt{L_1} + \sqrt{L_2})^2$ .

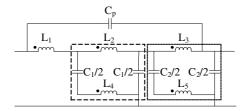

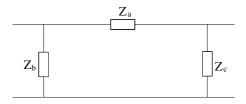

By performing the Y- $\Delta$  transformation,  $\pi$ -equivalent circuit of Figure 4 is illustrated in Figure 5. The equivalent parameters can be expressed as:

$$Z_{a} = \frac{j\omega(\sqrt{L_{de}} + \sqrt{L_{3}})^{2}}{1 - \omega^{2} \left[ C_{p}(\sqrt{L_{de}} + \sqrt{L_{3}})^{2} - C_{1}\sqrt{L_{de}L_{3}} \right]}$$

$$Z_{b} = \frac{(\sqrt{L_{de}} + \sqrt{L_{3}})^{2}}{j\omega C_{1}(L_{3} + \sqrt{L_{de}L_{3}})}$$

(2)

(3)

$$Z_b = \frac{(\sqrt{L_{de}} + \sqrt{L_3})^2}{j\omega C_1(L_3 + \sqrt{L_{de}L_3})}$$

(3)

Figure 5.  $\pi$ -equivalent circuit.

$$\frac{(\sqrt{L_{1}} + \sqrt{L_{2}} + \sqrt{L_{3}})^{2}}{(\sqrt{L_{1}} + \sqrt{L_{2}} + \sqrt{L_{3}})C_{p}}$$

$$\frac{(\sqrt{L_{1}} + \sqrt{L_{2}} + \sqrt{L_{3}})C_{p}}{\sqrt{L_{1}} + \sqrt{L_{2}} + \sqrt{L_{3}})C_{p} + C_{2}}$$

Figure 6. Ideal parasitic capacitance cancellation case.

$$Z_c = \frac{\sqrt{L_{de}} + \sqrt{L_3}}{j\omega C_1 \sqrt{L_{de}} + j\omega C_2 (\sqrt{L_{de}} + \sqrt{L_3})}$$

(4)

Therefore, the general parasitic capacitance cancellation condition can be derived as:

$$C_1 = \frac{(\sqrt{L_{de}} + \sqrt{L_3})^2}{\sqrt{L_{de}L_3}} C_p = \frac{(\sqrt{L_1} + \sqrt{L_2} + \sqrt{L_3})^2}{(\sqrt{L_1} + \sqrt{L_2})\sqrt{L_3}} C_p = C_r$$

(5)

when (5) is satisfied,  $Z_a$  in (2) becomes  $j\omega(\sqrt{L_1}+\sqrt{L_2}+\sqrt{L_3})^2$ , which is equivalent to the series impedance of an ideal inductor. As a result, the degradation of filter attenuation performance at high frequencies can be prevented. The  $\pi$ -equivalent circuit of ideal parasitic capacitance cancellation case is shown in Figure 6. In practical applications, the CM capacitance is approximately equals to the value of  $C_2$  because  $C_p$  is much smaller in contrast. Actually, the exterior ground winding part only contributes to low impedance path to ground while the interior part plays a key role in parasitic capacitance cancellation. Moreover, comparing with the original L-shape circuit, the  $\pi$ -network with forward shunt-capacitance provided by the cancellation winding can somewhat further improve the HF attenuation.

#### 3. SPLIT GROUND WINDING DESIGN

Based on the aforementioned analysis, the modeling, formulation and design procedure of proposed integrated EMI filter are described below.

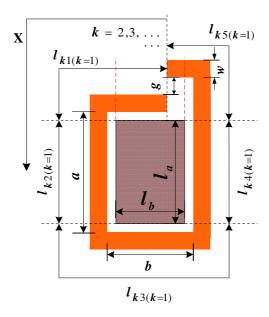

Figure 7. Top view of conductor winding.

# 3.1. Winding Modeling

A generalized top view of conductor winding wound around E core is shown in Figure 7, where  $a \times b$  are the internal dimensions of spiral wound conductors; w is the width of winding; g is the distance between adjacent turns;  $l_a \times l_b$  are the section dimensions of middle leg core. The winding length of the kth turn is  $l_k$ , and its physical meaning can be seen in Figure 7. k=1 winding turn is shown and followed by  $k=2,3\ldots$  winding turns with a similar configuration. Since the lateral dimension of planar spiral windings has to be considered,  $l_{k(k=1,2\ldots)}$  are different and need to be calculated accordingly as expressed in (6).

$$l_k = \begin{cases} 2a + 2b + 13w/2 + g - l_b/2 & k = 1\\ 2a + 2b + (8k - 3)w + (8k - 7)g & k > 1 \end{cases}$$

(6)

where k indicates the sequence of winding turns.

For most practical planar spiral winding inductors with planar E cores, the overhangs are not surrounded by a magnetic core; its inductance variation is much smaller than that of the conductors in the core window. When concerning the inductance characteristic which associated with proposed parasitic cancellation method, each turn is divided into five parts along X direction, as illustrated in Figure 7. It implies  $l_k$  is the total length given by the addition of  $l_{kq}$  (q indicates

the sequence of winding branches, range from 1 to 5), where  $l_{kq}$  is the length of each branch calculated as follows:

$$l_{kq} = \begin{cases} l_k - \sum_{q=2}^{5} l_{kq} & q = 1 \\ l_a & q = 2 \\ a + b + (4k - 2)w + (4k - 4)g - l_a & q = 3 \\ l_a & q = 4 \\ a/2 + b/2 + (2k + 1)w + (2k - 1)g - l_a/2 - l_b/2 & q = 5 \end{cases}$$

For planar filter design, the inductance could be calculated by using the following equation:

For planar filter design, the inductance could be calculated by using the following equation:

$$L = \mu_0 \mu_e n_{eff}^2 A_e / l_e \tag{8}$$

where  $\mu_e$  is the equivalent relative permeability of the magnetic core,  $n_{\it eff}$  the effective number of turns,  $A_e$  the effective area of the core, and  $l_e$  the core effective length.

As the electromagnetic and geometric points of view on the definition of number of turns are inconsistent,  $n_{eff}$  along X direction can be defined as a piecewise function.

$$\begin{cases} k-1 & 0 \leq X < \sum_{q=1}^{1} l_{kq} \\ k-1 + \frac{X - \sum_{q=1}^{1} l_{kq}}{2l_{k2}} & \sum_{q=1}^{1} l_{kq} \leq X < \sum_{q=1}^{2} l_{kq} \\ k-1/2 & \sum_{q=1}^{2} l_{kq} \leq X < \sum_{q=1}^{3} l_{kq} \\ k-1/2 + \frac{X - \sum_{q=1}^{3} l_{kq}}{2l_{k4}} & \sum_{q=1}^{3} l_{kq} \leq X < \sum_{q=1}^{4} l_{kq} \\ k & \sum_{q=1}^{4} l_{kq} \leq X < l_{k} \end{cases}$$

$$(9)$$

Since the voltage follows the same trend as the inductance changes according to Ohm's law, the voltage difference between two vertically adjacent conductors in multi-layer winding is a constant. The lumped

equivalent structural capacitance can be well estimated as:

$$C_p = \frac{\sum_{k=1}^m \frac{\varepsilon_0 \varepsilon_{in} w}{t} l_k (2k-1)^2}{(2m)^2} \tag{10}$$

where m is number of turns per layer, t the insulation thickness, and  $\varepsilon_{in}$  the relative permittivity of the insulation material. The accuracy of (10) has been proven by Chen et al. in [6].

# 3.2. Design Procedure

The effective optimal parameters to control  $C_1$  and obtain the desired capacitance  $C_r$  include the area of cancellation winding, the thickness and permittivity of dielectric layer. For safety reasons, the CM filter capacitance is normally limited to a few thousands of picofarads (pF) due to restricted ground leakage current. However, the modification on dielectric layer will certainly cause CM capacitance ( $\approx C_2$ ) changes at the same time. The safety requirement then cannot be guaranteed. Hence turning the area of interior ground winding part is considered as a more realistic solution. Assuming the width of ground conductor is fixed and equal to that of CM inductor layer, the length of interior winding along X direction  $X_1$  can be chosen as the design variable.

The ground capacitance formed by interior winding part is given by:

$$C_1 = \varepsilon_0 \varepsilon_{di} w X_1 / d \tag{11}$$

where  $\varepsilon_{di}$  and d are the relative permittivity and thickness of dielectric, respectively.

As all planar conductor windings are wound around the same middle core leg, their inductances are proportional to square of the effective number of turns accordingly, which can be drawn from (8).

$$L_1 \propto m^2$$

,  $L_2 \propto n_{eff}^2$ ,  $L_3 \propto (m - n_{eff})^2$  (12)

Therefore the required capacitance used for parasitic capacitance cancellation in (5) can be further simplified as:

$$C_r = \frac{4m^2}{m^2 - n_{eff}^2} C_p \tag{13}$$

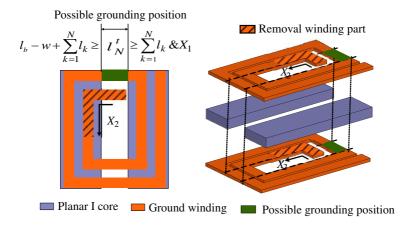

As  $C_1$  and  $C_r$  both are expressed as a function of  $X_1$ , make them equal to each other, the optimized value of  $X_1$  can be solved. However, there still exist the structural constraints since two planar I cores are commonly used as leakage layer. Considering convenience in implementation, the added grounding wire can only be tapped at a possible position, as an example layout shown in Figure 8.

Figure 8. An example layout of possible grounding position.

An alternative solution applied here is to determine the least number of turns of interior winding part N and grounding point firstly. The selection principle is to ensure the total winding length  $l_N^t$  has a value no less than  $X_1$  and  $\sum_{k=1}^N l_k$ , at the same time no greater than  $l_b+w+\sum_{k=1}^N l_k$ , which is based on a consideration of possible grounding point. It should be noticed that  $l_N^t$  is not necessarily be the same as  $\sum_{k=1}^N l_k$  unless the rightmost possible grounding point is chosen. The next step is to make the interior winding length of removal part along X direction  $X_2$  turn into the new optimized valuable. The relations above can be re-expressed as:

$$C_1 = \varepsilon_0 \varepsilon_r w \left( l_N^t - X_2 \right) / d \tag{14}$$

$$L_1 \propto (m + n_{eff})^2$$

,  $L_2 \propto (N - n_{eff})^2$ ,  $L_3 \propto (m - N)^2$  (15)

$$C_r = \frac{4m^2}{m^2 - N^2} C_p \tag{16}$$

Following a similar analysis to the previous case, the optimized value of  $X_2$  can be obtained. The problem caused by structural limitation is thus overcome without introducing too many processes. Since the required capacitance for parasitic capacitance cancellation  $(C_g)$  is only relevant with the value of EPC  $(C_p)$  and the turns-ratios of conductor windings according to (13) and (16), the effectiveness of parasitic capacitance cancellation depends primarily on geometry in this case.

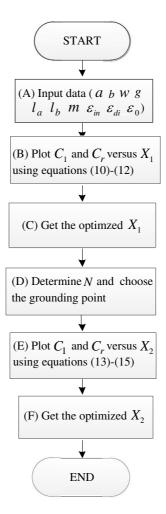

As stated in Figure 9, the flowchart of design procedure which consists of 6 main workflows (A)–(F) is implemented using the

Figure 9. Design procedure for split ground winding.

Table 1. Materials used in filter design.

| Item     | Magnetic core | Insulator | Dielectric | Conductor |

|----------|---------------|-----------|------------|-----------|

| Material | 3E5           | Kapton    | Ceramic    | Copper    |

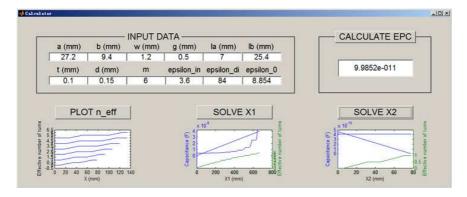

mathematical software package Matlab. It thus allows for efficient prototyping and quick modification of filter design. Once the structural and material parameters are known, it is easy to obtain the optimized layout of ground winding.

| a  (mm) | b (mm) | w  (mm) | g  (mm)          | $l_a \text{ (mm)}$ | $l_b \text{ (mm)}$ |

|---------|--------|---------|------------------|--------------------|--------------------|

| 27.2    | 9.4    | 1.2     | 0.5              | 7                  | 25.4               |

| t  (mm) | d (mm) | m       | $arepsilon_{in}$ | $\varepsilon_{di}$ | $\varepsilon_0$    |

| 0.1     | 0.15   | 6       | 3.6              | 84                 | 8.854              |

Table 2. Input data.

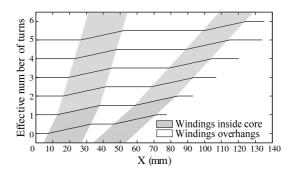

Figure 10. Effective number of turns  $n_{eff}$  along X direction.

It should be pointed out that the modification on ground layer does not change the DM components; therefore DM performance will be maintained in this design.

# 3.3. Implementation

In implementation, a planar E38 + PLT38 core surrounded by two identical integrated LC windings is used in the proposed integrated CM filter. The conductor thickness is  $0.3\,\mathrm{mm}$  for inductor layer and  $0.1\,\mathrm{mm}$  for ground layer due to power capability consideration. Table 1 list the materials used in the designed integrated CM filter prototype. Meanwhile, the input data of design procedure which cover all required parameters are summarized in Table 2.

As discussed previously, the effective number of turns  $n_{eff}$  along X direction can be clearly observed from Figure 10. The shaded regions displayed in following graphs can help to make the design processes more visual.

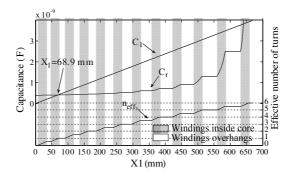

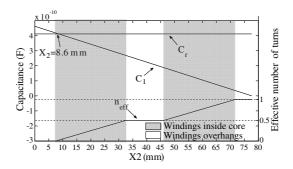

For the parameters used by the designed integrated CM filter prototype, the relationship of capacitances  $C_1$  and  $C_r$  as a function of  $X_1$  is plotted in Figure 11. The point where the two lines cross indicates the optimal design point, and the corresponding  $X_1$  turns out to be 68.9 mm. As the point of intersection is located within the second

Figure 11. Capacitances  $C_1$  and  $C_r$  versus  $X_1$ .

Figure 12. Capacitances  $C_1$  and  $C_r$  versus  $X_2$ .

"windings inside core" region, the number of turns of interior winding N is then determined to be one, and the rightmost possible position is chosen to be the grounding point. Likewise, the updated functions of capacitances  $C_1$  and  $C_r$  versus  $X_2$  are plotted in Figure 12 based on the chosen configuration. The optimized value of  $X_2 = 8.6\,\mathrm{mm}$  is then identified as the designed removal length of interior ground winding. With the single integrated GUI window shown in Figure 13, it is straightforward to prepare and execute the calculations.

According to the calculated results, the layout of split ground winding in the proposed integrated EMI filter is finally shown in Figure 14(a). The front cross-section view of half winding window and explored view are shown in Figures 14(b)–(c), respectively. It is also noted that within the operating frequency band, the CM performance is not sensitive to the distance between the end point of interior winding and the start point of exterior winding along X direction, thus a 1-mm-wide gap is acceptable in the filter prototype.

Figure 13. Matlab GUI window..

**Table 3.** Parameters of the designed CM filer.

| $L_{CM}$ (mH) | $C_{CM}$ (nF)  | Profile (cm) | Volume (cm <sup>3</sup> ) |

|---------------|----------------|--------------|---------------------------|

| 4.5           | $2 \times 3.7$ | 1.2          | 20                        |

### 4. EXPERIMENTAL RESULTS

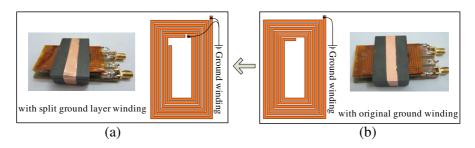

Applying the proposed method, an integrated CM filter with split winding structure is designed and constructed as shown in Figure 15(a). As contrast, Figure 15(b) shows the one with original ground winding. To reduce the influence of other parasitic pa

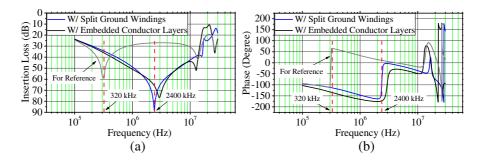

The parameters of the designed integrated CM filter are given in Table 3. By using an Advantest R3770 network analyzer, the insertion loss and phase characteristics of the filter with split winding structure are measured. The signal source impedance and the load impedance are set to real 50 Ohm standard value. Performance of the filter with original ground layer is also given for reference. The curves shown in Figure 16 confirm the first self-resonant frequency of the CM choke shifts from 320 kHz to more than 2400 kHz, which corresponding to  $\frac{1}{2\pi\sqrt{LC_p}}$ . It is also about fifty-six times decrease in EPC since f=evident that while the proposed integrated CM filter with split ground structure did not increase the number of layers; its characteristic is as good as the one with embedded conductor layers over a wider frequency range. However, the resonance showed up at around 20 MHz makes the performance at higher frequencies suffers notable degradation. It can be further damped out by increasing the HF winding losses and dielectric loss, which is beyond the scope of this paper.

There are some potential reasons to explain the phenomenon of

**Figure 14.** Designed structure. (a) Layout of designed split ground winding, (b) front cross-section view of half winding window, (c) explored view.

Figure 15. Constructed prototypes.

**Figure 16.** Performance of the integrated CM filters. (a) Insertion Losses, (b) phases.

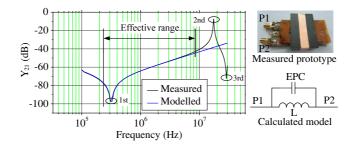

Figure 17. Measured and modeled  $Y_{21}$  of CM inductor prototype.

decreased attenuation. Firstly, in the analysis above, mutual couplings and winding conductance are assumed to be ideal. In fact, these assumptions are impossible to be satisfied in the real application, especially at high frequencies. Therefore, it can be predicted that HF suppression will be compromised to a certain degree. In addition, the computed admittance of the inductor model in Figure 17 reveals that EPC only reflects the first parallel resonance between inductor and the parasitic capacitance. However, when the interested frequency is very wide, for example 150 kHz to 30 MHz, there would be more series and parallel resonances observed at high frequencies, as shown by the measured  $Y_{21}$  curve of CM inductor prototype. In this case, the inductor cannot be represented using the simple model in Figure 3 anymore. So the parasitic capacitance cancellation will only work for the parasitic capacitance with first-order approximation, which is similar to the previous strategies.

#### 5. CONCLUSION

The design method using split ground structure to cancel the effects of parasitic winding capacitance is discussed in this paper. Without adding any additional components, the new approach has the advantage of simplicity which results in reduced fabrication time and cost. The first-order equivalent circuit is derived to demonstrate the parasitic capacitance cancellation mechanism, and structural limitation is also considered. Besides, the GUI has been developed and implemented in Matlab to efficiently design the split ground layer. Experimental results are presented to verify the theory in implementation and the application of proposed technology to an integrated CM filter.

## ACKNOWLEDGMENT

This work is supported by the National Natural Science Foundation of China under Grant 61071056 and Research Fund for the Doctoral Program of Higher Education of China under Grant 20090172120009.

#### REFERENCES

- 1. Ozenbaugh, R. L., *EMI Filter Design*, 2nd edition, Marcel Dekker, New York, 2001.

- 2. Lee, F. C., J. D. Van Wyk, Z. X. Liang, R. Chen, S. Wang, and B. Lu, "An integrated power electronics modular approach: concept and implementation," *Power Electronics and Motion Control Conf.*, Vol. 1, 1–13, Xi'an, China, Aug. 2004.

- 3. Chen, R., "Integrated EMI filters for switch mode power supplies," Ph.D Dissertation, Virginia Tech, Blackburg, Nov. 2004.

- 4. Chen, R., J. D. Van Wyk, S. Wang, and W. G. Odendaal, "Planar electromagnetic integration technologies for integrated EMI filters," *Proc. of the IEEE Industry Application Conf.*, Vol. 3, 1582–1588, Salt Lake City, Utah, Oct. 2003.

- 5. Chen, R., S. Wang, J. D. Van Wyk, and W. G. Odendaal, "Integration of EMI filter for distributed power system (DPS) front-end converter," *Proc. of the IEEE PESC'03*, Vol. 3, 1582–1588, 2003.

- 6. Chen, R., J. D. Van Wyk, S. Wang, and W. G. Odendaal, "Improving the characteristics of integrated EMI filters by embedded conductive layers," *IEEE Trans. on Power Electron.*, Vol. 20, No. 3, 611–619, May 2005.

- 7. Jiang, Y., S. Wang, F. C. Lee, and J. D. Van Wyk, "Equivalent parallel capacitance cancellation for noise reduction application," *Applied Power Electronics Conf. and Expo.*, 745–750, Austin, Texas, Feb. 2008.

- 8. Tsai, H.-C., "Numerical and experimental analysis of EMI-induced noise in RC phase shift oscillator," *Progress In Electromagnetics Research*, Vol. 122, 223–244, 2012.

- 9. Wang, S., R. Chen, J. D. Van Wyk, F. C. Lee, and W. G. Odendaal, "Developing parasitic cancellation technologies to improve EMI filter performance for switching mode power supplies," *IEEE Trans. on Electromagn. Compat.*, Vol. 47, No. 4, 921–929, Nov. 2005.

- 10. Neugebauer, T. C. and D. J. Perreault, "Parasitic capacitance cancellation in filter inductors," *IEEE Trans. on Power Electron.*, Vol. 21, No. 1, 282–288, Jan. 2006.

- 11. Neugebauer, T. C. and D. J. Perreault, "Parasitic capacitance cancellation in filter inductors," *Proc. of the IEEE PESC'04*, Vol. 4, 3102–3107, 2004.

- 12. Wang, S., F. C. Lee, and J. D. Van Wyk, "Design of inductor winding capacitance cancellation for EMI suppression," *IEEE Trans. on Power Electron.*, Vol. 21, No. 6, 1825–1832, Nov. 2006.

- 13. Wang, S., F. C. Lee, and J. D. Van Wyk, "Inductor winding capacitance cancellation using mutual capacitance concept for noise reduction application," *IEEE Trans. on Electromagn. Compat.*, Vol. 48, No. 2, 311–318, May 2006.

- 14. Wang, S., F. C. Lee, D. Y. Chen, and W. G. Odendaal, "Effects of parasitic parameters on EMI filter performance," *IEEE Trans. on Power Electron.*, Vol. 19, No. 3, 869–877, May 2004.

- 15. Wang, S. and F. C. Lee, "Common mode noise reduction for power factor correction circuit with parasitic capacitance cancellation," *IEEE Trans. on Electrom. Compat.*, Vol. 49, No. 3, 537–542, 2007.

- 16. Wang, S. and F. C. Lee, "Investigating parasitic capacitance cancellation for EMI suppression," *Vehicle Power and Propulsion Conf.*, 954–961, Sep. 2009.

- 17. Wang, S. and F. C. Lee, "Analysis and applications of parasitic capacitance cancellation techniques for EMI suppression," *IEEE Trans. on Industrial Electron.*, Vol. 57, No. 9, 3109–3117, Sep. 2010.

- 18. Wang, S. and F. C. Lee, "Common mode noise reduction using parasitic capacitance cancellation," US Patent 7602 159 B2, Oct. 13, 2009.