# FPGA IMPLEMENTATION OF SPACE-TIME ADAPTIVE PROCESSING (STAP) ALGORITHM FOR TARGET DETECTION IN PASSIVE RADARS

Zia Ul Mahmood<br/>1, \*, Mubashir Alam¹, Khalid Jamil², and Zeyad O. Al-Hekail¹, ²

<sup>1</sup>Department of Electrical Engineering, King Saud University, Riyadh, Saudi Arabia

<sup>2</sup>Prince Sultan Advanced Technologies Research Institute, King Saud University, Riyadh, Saudi Arabia

Abstract—Space-Time Adaptive Processing (STAP) algorithm has recently been used in Passive Bi-static Radars (PBR) because it removes the clutter and non-cooperative transmitter effectively making the target detection easy in harsh environments like air-ground. Real-time implementation of STAP is a very challenging task as it is computationally-intensive, time-critical and resource-hungry process. This paper focuses on the Field-Programmable Gate Array (FPGA) implementation of STAP algorithm for passive radar using FM radio as transmitter of opportunity. The signals of interest were collected using an eight-channel software-defined radar with a uniform circular array (UCA). The STAP processing was simulated using MATLAB and hardware implementation was carried out on a Xilinx Virtex-6 FPGA. The system is tested using experimental radar data. Timing and Power analysis of hardware implementation justifies that FPGA provides a fast and reliable platform for STAP real-time radar processing.

#### 1. INTRODUCTION

Passive bi-static radars (PBR) has received significant interest during the past few years among various defense entities for surveillance and defense applications. These radars exploit signals of opportunity from a wide variety of communication or broadcast emissions like FM, TV, GSM, DAB, DVB-T, WiMax, WLAN/WiFi, satellite, etc. [12–18,24]. They offer a number of advantages over conventional active

Received 10 October 2012, Accepted 29 November 2012, Scheduled 30 November 2012

<sup>\*</sup> Corresponding author: Zia Ul Mahmood (zmahmood@ksu.edu.sa).

radar system: reduced operational cost, lower power requirements, covertness and anti-stealth.

A typical passive radar system consist of two channels connected with two antennas. One antenna, labeled as reference antenna, captures the direct (reference) signal from the transmitter. A second antenna captures the reflected signal from target. These two signals are processed together for target detection using match-filtering like cross-ambiguity processing [8, 9, 16, 23].

A more sophisticated multi-channel multi-frequency digital receiver system is developed using an array of antennas [19]. This type of advance system gives additional capabilities like digital beamforming and advance adaptive filtering for target detection and clutter rejection [9, 19, 20]. One of the candidate adaptive algorithm for this kind of radar processing is joint space-time adaptive processing (STAP). It is particularly useful in detecting weak and slow moving ground targets in airborne clutter environments.

Much of the research has been done on STAP with active radars using uniform linear array (ULA) [3, 10, 11] and circular array [4, 5, 7]. Some of the research exists on the clutter suppression of airborne radar [25–27]. Similarly, some adaptive filter algorithms were used for clutter cancellation in PBR [22]. A code was designed to maximize the detection performance of radar STAP [21]. A limited research exists on using STAP for a passive radar system. One such system and algorithm is presented in [8, 9], which uses a receiver setup of two antenna system to capture the signal of interests. Further research was conducted in an attempt to develop a more advanced receiver setup like ULA [1, 2] and UCA [6, 19, 20]. There is no notable research available on the FPGA implementation of STAP algorithm for PBR case while using UCA for effective target detection and tracking.

This paper presents modeling and implementation of STAP algorithm for target detection in passive bistatic radar case using a uniform circular array to capture the signals of interest. The antenna array consists of eight elements with uniform radial spacing. The UCA geometry is deployed due to its ability to steer the beam in azimuth digitally through 360° without any mechanical movement [6]. Also, a cooperative FM transmitter was used as an illuminator of opportunity. The actual experiment was performed with moving vehicle as a target.

This paper emphasizes the hardware implementation aspect of STAP algorithm in PBR. System model containing the data reception scenario and the pre-processing steps are explained in Section 2. The processing results are described in Section 3. Section 4 explains the FPGA implementation of the STAP processor. Concluding remarks are given in Section 5.

#### 2. DATA RECEPTION SCENARIO

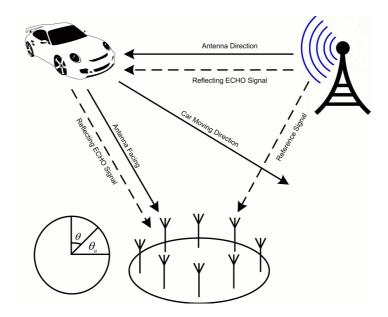

The experimental setup consists of an FM transmitter, a moving vehicle as a target and a circular eight-element antenna array as shown in Fig. 1. This is used to record the eight real time signals separately impinging on each antenna element of the uniform circular array.

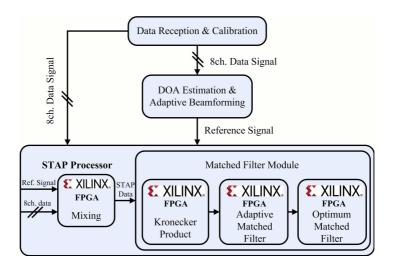

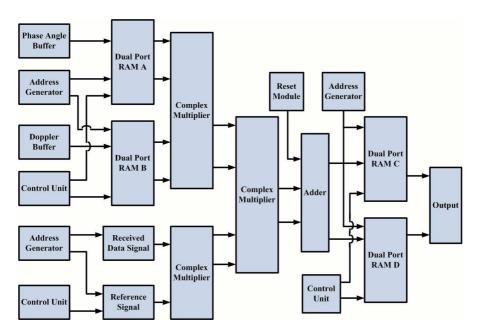

The signal processing block diagram is shown in Fig. 2 to elaborate the system setup. Pre-processing includes the calibration of phase and amplitude errors of the eight-channel real-time FM data. The calibrated array data are then subjected to Direction-of-Arrival (DOA) estimation and adaptive digital beam-forming in order to obtain pure reference signal from the transmitter without any echo return from targets. The pure reference and the eight-channel data containing the echoes from the targets is then used for STAP processing.

## 2.1. STAP Processing

The STAP processing needs a pure reference signal and eight channel data signal as its inputs. The algorithm used was the one presented in [8], with one major improvement in the term of multi-element circular array geometry, to achieve more flexibility and coverage. The mixing module as shown in Fig. 2 is used to combine the eight channel

Figure 1. Data reception scenario.

**Figure 2.** Signal processing block diagram of an array based passive radar.

data signal with time delayed version of the pure reference signal,  $\mathbf{x_{ref}}(k-n)$ . For the specific case of UCA, the spatial steering vector and temporal steering vector are given by (1) and (2) respectively.

$$\mathbf{a}(v_s) = \left[ e^{(j\beta R\cos(\theta_1 - \theta))}, \dots, e^{(j\beta R\cos(\theta_N - \theta))} \right]^T \tag{1}$$

$$\mathbf{b}(v_d) = \left[1, e^{j2\pi v_d}, \dots, e^{j2\pi v_d(M-1)}\right]^T \tag{2}$$

where  $\beta = \frac{2\pi}{\lambda}$  and  $\lambda$  is the wave-length, R the radius of the array. The angular position of each element in the array is given by  $\theta_n = \frac{2\pi n}{N}$ , where N is the number of antenna elements, and  $\theta$  the incidence angle or the scanning angle. The spatial frequency is given by  $v_s = \beta R \cos(\theta_n - \theta)$  and  $v_d = \frac{f_d S}{f_s}$  is the reduced Doppler frequency, where  $f_d$  the Doppler frequency of the target, S and S denote the subsampling factor and sampling frequency respectively [8]. The combined spatio-temporal steering vector is given by:

$$\mathbf{v}(v_s, v_d) = \mathbf{a}(v_s) \otimes \mathbf{b}(v_d) \tag{3}$$

The size of the spatio-temporal steering vector depends on the temporal samples M and the number of antenna elements N used in the circular array. This spatio-temporal steering vector or the scanning vector  $\mathbf{v}(v_s, v_d)$  will be used to scan the eight channel data denoted by  $\mathbf{x}(k)$ . At some specific range n, data received on each channel of array

is mixed with the time-delayed version of the reference signal. This mixing product  $\mathbf{x_m}(k;n)$  is given by:

$$\mathbf{x_m}(k;n) = \mathbf{x}(k) \circ (1 \otimes \mathbf{x_{ref}}(k-n))^* \tag{4}$$

The mixing product was sub-sampled to obtain the lexically ordered sub-sampled signal  $\mathbf{x}_{\mathbf{s}}(n)$  given by [8]:

$$\mathbf{x_s}(n) = \left[\mathbf{x_m^T}(0; n), \mathbf{x_m^T}(S; n), \dots, \mathbf{x_m^T}((M-1)S; n)\right]^T$$

(5)

To find the angle-Doppler information of targets and main transmitter (clutter) from the received data, matched filtered output  $y_m$  can be calculated by using spatio-temporal steering vector in (3) and the sub-sampled signal in (5), which is given by:

$$y_m(v_s, v_d; n) = \mathbf{v}^{\dagger}(v_s, v_d) \mathbf{x_s}(n) \tag{6}$$

where,  $\dagger$  represents Hermitian transpose operation. The last step in STAP processing, optimum matched filtering, was used to filter out the clutter contributions consisting of transmitter signature at zero Doppler frequency to get the target signature. This processing requires the calculation of interference and noise covariance matrix R. The model covariance matrix was used in our simulation. Many other approaches exist for calculating a more precise covariance matrix [8]. The optimum matched filter output can be calculated as:

$$y(v_s, v_d; n) = \mathbf{w}^{\dagger}(v_s, v_d) \mathbf{x_s}(n) \tag{7}$$

where,  $\mathbf{x_s}(n)$  is the recorded sub-sampled signal and  $\mathbf{w}$  is the optimum filter weight vector given by

$$\mathbf{w}(v_s, v_d) = R^{-1} \mathbf{v}(v_s, v_d) \tag{8}$$

where, R is the estimate of the interference covariance matrix. In practical, estimation of R requires large number of training data samples, and also is very difficult to estimate in the case of passive radar from actual data. Therefore, a model interference covariance matrix was used for this scenario [8, 28].

The basic steps involved in the STAP process from data reception to target detection are given by:

- First, the eight channel data signal received from the circular antenna array is pre-processed in order to remove the mutual coupling effects and apply the phase and amplitude correction [19].

- The pure reference signal is extracted from the received array data using adaptive beamforming [20].

- The eight channel data signal is mixed with the pure reference signal using the mixing product using (4).

• The spatial and temporal steering vectors given by (1) and (2) are used to calculate spatio-temporal steering vector also known as scanning vector given by (3).

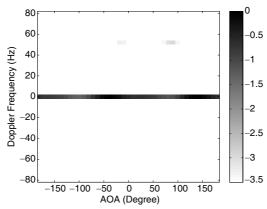

- Matched filtering of (3) and (5) is performed in order to obtain angle-Doppler information of the targets and interferences using (6) as shown in Fig. 3.

- Interference covariance matrix is calculated to obtain the weight vector which suppresses the zero-Doppler direct path interferer given by (8).

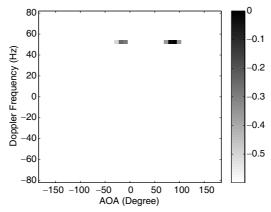

- Finally, the weight vector is used by optimum matched filtering given by (7), in order to get pure target signature as shown in Fig. 4.

Figure 3. Matched filter output.

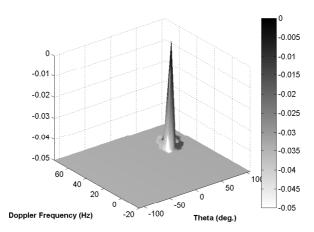

Figure 4. Optimum matched filter output.

#### 3. DATA PROCESSING RESULTS

All the signal processing steps in Fig. 2, were first implemented in MATLAB environment which will be discussed in this section. Secondly, the signal processing steps for STAP processor, implemented on Xilinx Virtex-6 FPGA will be discussed in Section 4. The data reception scenario contains a non-cooperative FM transmitter at 924 MHz installed 600 meters away from the circular antenna array. A single target vehicle, moving towards the array at around  $90^{\circ}$  with a speed of  $60 \, \text{km/h}$ . After receiving the eight channel signal, post-processing of the data was performed using MATLAB. This results in separating the pure reference signal from the received eight channel data signal [20]. The reference and eight-channel data signals are then fed to STAP processor. The adaptive matched filter output using (6) is shown in Fig. 3, which confirms the transmitter at  $-30^{\circ}$  with zero-Doppler frequency and a very weak moving target signature at  $90^{\circ}$  with  $52 \, \text{Hz}$  Doppler.

Optimum matched filtering using (7) is then used to effectively remove the zero-Doppler frequency components as shown in Fig. 4, and leaving the very strong target signature.

Figure 5. STAP processing blockset designed for FPGA.

#### 4. HARDWARE IMPLEMENTATION

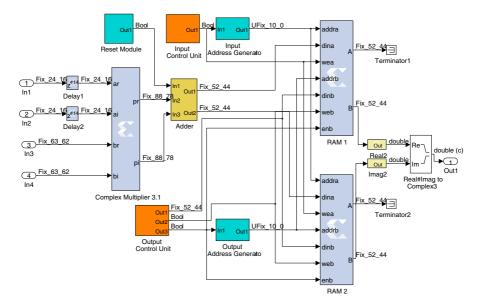

The challenging part of our research lies in the FPGA implementation of STAP algorithm on passive bistatic radar using uniform circular array. We want to develop a compact, light-weight and high-speed passive radar system on which STAP algorithm can be implemented. In this paper, Xilinx Virtex-6 FPGA was used to design the data processing steps of STAP, as shown in Fig. 5; initially for post-processing of the received data.

The designed model includes phase-angle and Doppler-bin buffers that scan the received data to find the respective target bearing angle and Doppler. Various control blocks were used to control the input data to perform respective tasks of STAP processor. Address generator block was used to assign the addresses to the input data when arrived at the input of dual-port RAM blocks. As the received data is complex, therefore, complex multipliers are needed for all multiplication operations. The adder block was used for multiplication operations to add every row of data and store the value at specific RAM address.

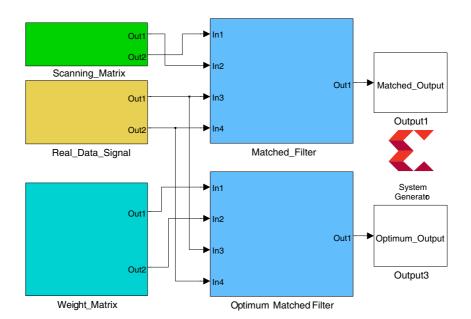

The FPGA implemented version of designed STAP processing block-set is shown in Fig. 6. The scanning matrix block-set generates

Figure 6. FPGA implemented STAP processing.

Figure 7. FPGA matched filter processing.

Figure 8. Hardware co-simulation model.

the spatial and temporal scanning vectors to identify estimated location of the target. The real data signal block-set generates the target signal mixing module process. The weight matrix block-set directly loads the required weights for optimum matched filtering. A basic matched filter processing blockset was designed as shown in Fig. 7 which was used by both matched filter and optimum matched filter blocksets as shown in Fig. 6. By changing the inputs and FPGA clock, the matched filter blockset was reused for optimum matched filtering.

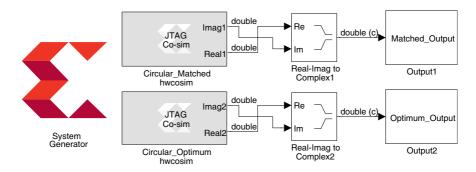

In order to run the STAP process directly over FPGA using Xilinx

Figure 9. Optimum matched filter output from FPGA.

**Table 1.** Resources and power utilization summary of matched filtering.

| On-Chip Components | Available | Matched Filtering |              | Power |

|--------------------|-----------|-------------------|--------------|-------|

| On-Chip Components |           | Used              | Utilized (%) | (W)   |

| Flipflops          | 301440    | 1993              | 0.7          | 0.09  |

| Slice LUT's        | 150720    | 1704              | 0.01         | 0.03  |

| Block RAM's        | 416       | 8                 | 1.9          | 0.125 |

| IO's               | 600       | 203               | 33.8         | 0.418 |

| DSP48E1's          | 768       | 40                | 5.2          | 0.039 |

| Leakage Power      | -         |                   |              | 3.443 |

| Total Power        | -         |                   |              | 4.145 |

System Generator, hardware co-simulation model as shown in Fig. 8 was needed which takes the received target data from computer and manipulates it separately with matched filtering and optimum matched filtering and transfers the result back to computer to display the angle-Doppler plot of the target as shown in Fig. 9. The obtained results are in good agreement with MATLAB processing result as shown in Fig. 4.

## 4.1. Hardware Timing and Power Analysis

The next step in FPGA implementation is to find out the computational and the power requirements. The results of the timing

| On-Chip       | Available | Optimum Matched Filtering |              | Power |

|---------------|-----------|---------------------------|--------------|-------|

| Components    | Available | Used                      | Utilized (%) | (W)   |

| Flipflops     | 301440    | 1283                      | 0.42         | 0.08  |

| Slice LUT's   | 150720    | 3197                      | 0.02         | 0.012 |

| Block RAM's   | 416       | 336                       | 80.77        | 0.068 |

| IO's          | 600       | 209                       | 34.83        | 0.248 |

| DSP48E1's     | 768       | 24                        | 3.125        | 0.011 |

| Leakage Power | -         |                           |              | 3.435 |

| Total Power   | -         |                           |              | 3.854 |

**Table 2.** Resources and power utilization summary of optimum matched filtering.

**Table 3.** Computation time and frequency analysis.

|                   | MATLAB     | FPGA       | Maximum     |  |

|-------------------|------------|------------|-------------|--|

| Processing        | Processing | Processing | FPGA        |  |

|                   | (sec)      | (nsec)     | Freq. (MHz) |  |

| Matched Filtering | 7          | 4.964      | 201.450     |  |

| Optimum Matched   | 9.8        | 9.944      | 100.563     |  |

| Filtering         | 9.0        | 9.344      | 100.005     |  |

and power analysis of matched filtering and optimum matched filtering are presented in Table 1 and Table 2 respectively. The results show that the process of matched filtering requires more power while utilizing less resources as compared to the process of optimum matched filtering which requires less power while utilizing more on-chip resources.

The timing analysis as shown in Table 3, shows a huge difference between MATLAB and FPGA processing time. It is also observed that the matched filtering process requires less FPGA clock period as compared to optimum matched filtering because it uses less resources as compared to optimum one. The maximum frequency required by FPGA depends on the FPGA clock period. The lesser the clock period of FPGA, greater will be the operating FPGA frequency and vice versa.

### 5. CONCLUSION

MATLAB Simulation and the hardware implementation of STAP algorithm for Passive Bi-static Radar (PBR) using uniform circular array was presented. This implementation was verified with the

real field experimental data using FM as transmitter of opportunity. The results are based on offline processing of the data, both for MATLAB and FPGA processing. The MATLAB processing results along with the FPGA output shows that the zero-Doppler clutter can be effectively filtered out by using optimum matched filtering. Future work will focus on real-time target detection using STAP processing to achieve a dedicated radar system for the proposed technique.

#### ACKNOWLEDGMENT

The above research has been sponsored by King Abdulaziz City for Science and Technology (KACST) under grant number 09-ELE-729-02 and D-S-12-0107.

#### REFERENCES

- 1. Ul Mahmood, Z., M. Alam, K. Jamil, and M. Elnamaky, "Implementation of space-time adaptive processing (STAP) for target detection in passive bi-static radar," *PIERS Proceedings*, 724–727, Kuala Lumpur, Malaysia, Mar. 27–30, 2012.

- 2. Ul Mahmood, Z., M. Alam, K. Jamil, and M. Elnamaky, "On modeling and hardware implementation of space-time adaptive processing (STAP) for target detection in passive bistatic radar," The 11th International Conference on Information Sciences, Signal Processing and Their Applications: Main Tracks (ISSPA2012-Tracks), 1040–1044, 2012.

- 3. Gong, Q. and Z.-D. Zhu, "Study STAP algorithm on interference target detect under non-homogenous environment," *Progress In Electromagnetics Research*, Vol. 99, 211–224, 2009.

- 4. Sarkar, T. K. and R. Adve, "Space-time adaptive processing using circular arrays," *Antennas and Propagation Magazine*, Vol. 43, No. 1, 138–143, 2001.

- 5. Zatman, M., "Circular array STAP," *IEEE Transactions on Aerospace and Electronic Systems*, Vol. 36, No. 2, 510–517, 2000.

- 6. Belfiori, F., S. Monni, W. Van Rossum, and P. Hoogeboom, "Side-lobe suppression techniques for a uniform circular array," *European Radar Conference (EuRAD)*, 113–116, 2010.

- 7. Nguyen, H. N., J. D. Hiemstra, and J. S. Goldstein, "The reduced rank multistage Wiener filter for circular array STAP," *Proceedings of the IEEE Radar Conference*, 66–70, 2003.

- 8. Neyt, X., J. Raout, M. Kubica, V. Kubica, S. Roques, M. Acheroy,

- and J. G. Verly, "Feasibility of STAP for passive GSM-based radar," *IEEE Conference on Radar*, 546–551, 2006.

- 9. Kubica, M., V. Kubica, X. Neyt, J. Raout, S. Roques, and M. Acheroy, "Optimum target detection using illuminator of opportunity," *IEEE Conference on Radar*, 417–424, 2006.

- 10. Melvin, W. L., "A STAP overview," Aerospace and Electronic Systems Magazine, Vol. 19, No. 1, 19–35, 2004.

- 11. Sarkar, T. K., H. Wang, S. Park, R. Adve, J. Koh, K. Kim, Y. Zhang, M. C. Wicks, and R. D. Brown, "A deterministic least-squares approach to space-time adaptive processing (STAP)," *IEEE Transactions on Antennas and Propagation*, Vol. 49, No. 1, 91–103, 2001.

- 12. Homer, J., K. Kubik, B. Mojarrabi, I. D. Longstaff, E. Donskoi, and M. Cherniakov, "Passive bi-static radar sensing with LEOS based transmitters," *IEEE International Geo-science and Remote Sensing Symposium*, (IGARSS), Vol. 1, 438–440, 2002.

- 13. Chetty, K., K. Woodbridge, G. Hui, and G. E. Smith, "Passive bi-static WiMAX radar for marine surveillance," *IEEE Radar Conference*, 188–193, 2010.

- 14. Colone, F., P. Falcone, C. Bongioanni, and P. Lombardo, "WiFi-based passive bi-static radar: Data processing schemes and experimental results," *IEEE Transactions on Aerospace and Electronic Systems*, Vol. 48, No. 2, 1061–1079, 2012.

- 15. Howland, P. E., D. Maksimiuk, and G. Reitsma, "FM radio based bi-static radar," *IEE Proceedings Radar, Sonar and Navigation*, Vol. 152, No. 3, 107–115, 2005.

- 16. Tan, D. K. P., H. Sun, Y. Lu, M. Lesturgie, and H. L. Chan, "Passive radar using global system for mobile communication signal: Theory, implementation and measurements," *IEE Proceedings Radar, Sonar and Navigation*, Vol. 152, No. 3, 116–123, 2005.

- 17. Berger, C. R., B. Demissie, J. Heckenbach, P. Willett, and S. Zhou, "Signal processing for passive radar using OFDM waveforms," *IEEE Journal of Selected Topics in Signal Processing*, Vol. 4, No. 1, 226–238, 2010.

- 18. Cai M., F. He, and L. Wu, "Application of UKF algorithm for target tracking in DTV-based passive radar," 2nd International Congress on Image and Signal Processing, (CISP), 1–4, 2009.

- 19. Jamil, K., M. Alam, M. Hadi, and Z. Alhekail, "A multi-band multi-beam software-defined passive radar Part I: System design," *IET Radar Conference*, 2012.

20. Alam, M., K. Jamil, Z. Alhekail, and S. Alhumaidi, "A multiband multi-beam software-defined passive radar Part II: Signal processing," *IET Radar Conference*, 2012.

- 21. De Maio, A., S. De Nicola, Y. Huang, D. P. Palomar, S. Zhang, and A. Farina, "Code design for radar STAP via optimization theory," *IEEE Transactions on Signal Processing*, Vol. 58, No. 2, 679–694, 2010.

- 22. Palmer, J. E. and S. J. Searle, "Evaluation of adaptive filter algorithms for clutter cancellation in passive bistatic radar," *IEEE Radar Conference (RADAR)*, 493–498, 2012.

- 23. Searle, S., S. Howard, and J. Palmer, "Remodulation of DVBT signals for use in passive bistatic radar," Conference Record of the Forty Fourth Asilomar Conference on Signals, Systems and Computers (ASILOMAR), 1112–1116, 2010.

- 24. Harms, H. A., L. M. Davis, and J. Palmer, "Understanding the signal structure in DVB-T signals for passive radar detection," *IEEE Radar Conference*, 532–537, 2010.

- 25. Yang, Z. C., Z. Liu, X. Li, and L. Nie, "Performance analysis of STAP algorithms based on fast sparse recovery techniques," *Progress In Electromagnetics Research B*, Vol. 41, 251–268, 2012.

- 26. Liu, Z., X. Wei, and X. Li, "Adaptive clutter suppression for airborne random pulse repetition interval radar based on compressed sensing," *Progress In Electromagnetics Research*, Vol. 128, 291–311, 2012.

- 27. Wu, D., Z. Xu, L. Zhang, Z. Xiong, and S. Xiao, "Performance analysis of polarization-space-time three-domain joint processing for clutter suppression in airborne radar," *Progress In Electromagnetics Research*, Vol. 129, 579–601, 2012.

- 28. Richards, M. A., Fundamentals of Radar Signal Processing, Tata McGraw-Hill Education, 2005.