# EMC COMPUTER MODELLING AND SIMULATION OF INTEGRATED CIRCUITS IN QFN PACKAGE

Haiyan Sun<sup>1, \*</sup>, Boyuan Zhu<sup>2</sup>, Ling Sun<sup>1</sup>, Hengxu Li<sup>2</sup>, and Lingling Yang<sup>1</sup>

<sup>1</sup>Jiangsu Key Laboratory of ASIC design, Nantong University, No. 9, Seyuan Road, Nantong, Jiangsu 226019, China

<sup>2</sup>School of Engineering, Griffith University, 170 Kessels Rd., Nathan, QLD 4111, Australia

Abstract—This paper discusses the application of computational electromagnetics (CEM) for electromagnetic compatibility (EMC) problems of integrated circuits (ICs). It is known that the application of CEM is versatile in solving a wide range of problems. This paper focuses on the electromagnetic study of quad flat non-lead (QFN) packaged ICs, one monolithic microwave integrated circuit (MMIC) and another radio frequency integrated circuit (RFIC), from the individual chip to system in package (SiP). Full-wave electromagnetic technique is conducted in the modelling and simulation. Both chips are found producing radiated emissions in horizontal directions as omnidirectional antennas at working frequencies and then directional at resonance frequencies.

#### 1. INTRODUCTION

Computational electromagnetic (CEM) modelling techniques [1] are now an integral part of design in engineering practice. They can be used to solve real life electromagnetic compatibility (EMC) problems and help industry to provide better products and equipment. Traditional EMC product testing needs a developed physical prototype or existing piece of equipment to be put in a test-house at the post-design stage, which is time consuming and expensive. By comparison, computational modelling and simulation is potentially considerable faster and cheaper. Furthermore it is also very flexible in allowing engineers to easily access, monitor and modify the area

Received 28 August 2013, Accepted 5 November 2013, Scheduled 9 November 2013

<sup>\*</sup> Corresponding author: Haiyan Sun (sun.yan@ntu.edu.cn).

of interest inside the design. Therefore, EMC computer modelling and simulation will play an important role in scientific research and industry applications.

According to a recent study, IC development is experiencing rapid growth and this is expected to continue [5]. Demands of scaling, performance and functionality drive IC design from traditional 2D configuration towards 3D assembly [6], which presents challenging EMC problems on different components (for example, packaging and interconnection). Due to the increasing clock speed, the size of the IC chip becomes comparable with the wavelength of interest, which makes it impossible to ignore the affects on electromagnetics. Modelling and analysis of electromagnetic behaviour for the IC becomes necessary, and CEM method provides good support in solving various problems.

EMC modelling and simulation of ICs require full-wave techniques in order to obtain a complete solution of Maxwell's equations within the computational domain for all materials and structures with arbitrary size. Recent publications [3,4] have verified the IC EMC modelling and simulation by means of a full-wave technique using commercial electromagnetic software package. In addition, IEEE standards association (IEEE-SA) has approved two new standards, IEEE 1597.1 and IEEE 1597.2, for validation of computational electromagnetics computer modelling and simulations. Those standards provide examples and problem sets to be used in the validation of CEM computer modeling and simulation techniques, codes, and models. It enhances the reliability of applying commercial electromagnetic software package for the analysis of a wide variety of electromagnetics applications.

This paper presents an electromagnetic research of two quad flat non-lead (QFN) packaged ICs which are rarely studied. Section 2 gives a brief literature review on the development and limitation of IC in planar structure. Section 3 presents the introduction of full-wave technique and challenge of QFN package. In Section 4 and 5, modelling and simulation of two QFN packaged ICs (MMIC and RFIC) are described in detail including all relevant results and followed by conclusions.

# 2. PROBLEM ANALYSIS OF PLANAR STRUCTURAL IC EMC

As early as the late 1950s, concerns about the performance of components operating under increasingly electromagnetic environments at the IC level existed and continued [2]. However, due to technology limitations, the EMC issues in the IC did not seem to be important

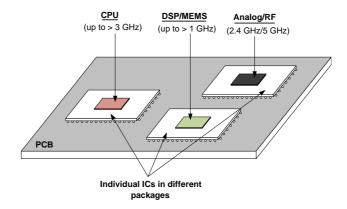

until the last decade. It was found that an IC was almost a miniature version of an EMC system, which contained the same coupling mechanisms as a large-scale system. As depicted in Figure 1, a system generally consists of different ICs with individual packages on the printed circuit board (PCB).

Figure 1. Individual ICs in different packages.

Driven by high clock speed and circuitry complexities, parasitic emissions in ICs contribute most of electromagnetic interference. Conducted emissions generated by faster and stronger transient current peaks escape from the digital core through silicon tracks, bonding wires and package lead frames. As a result, unwanted radiation may occur during propagation. The electromagnetic field, which radiates directly by internal silicon circuit routines or a package frame, is another form of interference (radiated emission). All these interferences will affect the performance and stability of adjacent components. As each chip is individually packaged, it requires a large system board to build a system that consumes a lot of power and introduces long signal propagation paths.

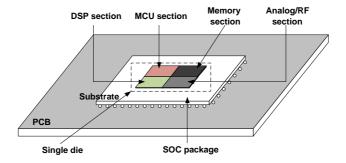

In order to reduce those risks, system-on-chip (SOC) is developed which integrates all components of a system into a single chip, as shown in Figure 2. It achieves a high integration of functions but increases the design complexity. A universal process will be used for all sections that makes each section can not be optimal for electromagnetics. In addition, once noise is coupled into the circuit, there is no way to isolate the problem as to the sections interact with each other.

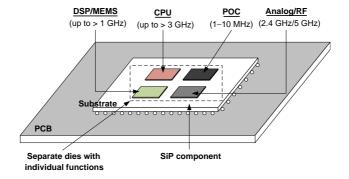

System in package (SiP) encloses a number of ICs in a single package. Traditional planar IC/SiP packages, as illustrated in Figure 3, separate dies horizontally inside the encapsulation. It overcomes the drawbacks previously discussed but it cannot avoid a

Figure 2. Example of a system-on-chip (SOC).

Figure 3. Example of a planar IC/SiP.

complicated internal electromagnetic environment due to discrepancies in functionality and the working frequency of each die [7]. Meanwhile, the planar architecture has limitations for future demand.

# 3. CEM MODELLING OF ICS IN QFN PACKAGE

# 3.1. Full-wave Techniques in the Frequency Domain

A full-wave electromagnetic solution, which solves electromagnetic problems with Maxwell's equations, is of great importance to high performance VLSI design in computational electromagnetics. With numerous fast numerical algorithms developed, the finite element method (FEM) is relatively efficient in finding approximate solutions of partial differential equations (PDE). The frequency domain vector wave equation for E field can be derived as:

$$\nabla \times \frac{1}{\mu} \nabla \times \vec{E} + \sigma_e \omega \vec{E} + \omega^2 \varepsilon \vec{E} = -j\omega \vec{J} \tag{1}$$

where  $\omega$  is the angular frequency, J is the source current density,  $\sigma_e$  is the effective conductivity, and  $\mu$  and  $\varepsilon$  are the permeability and permittivity of the problem space respectively.

Simulations in the followed discussion are applied by a full-wave frequency domain solution with variable sized meshes. Frequency is set up to sweep in a specific range to determine the expectant resonant frequency. However, determining the correct frequency range is important for simulation results. Computational errors may be introduced if the frequency range of the solution is mismatched.

# 3.2. ICs in QFN Package and Challenge

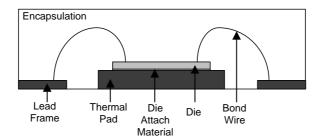

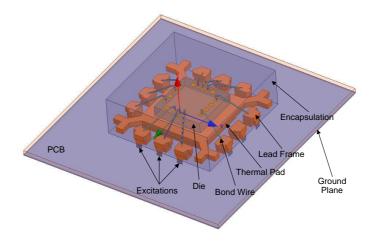

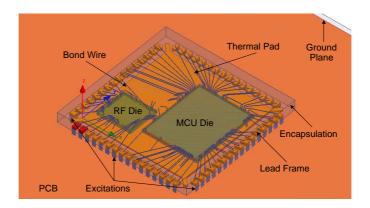

The QFN package is referred as a surface-mount technology which provides physical and electrical connection of an IC directly onto the surface of the PCB with no through-holes. As shown in Figure 4, a cross section of one typical QFN chip is presented. The lead frame provides connections to the external PCB. The internal connections between the die and lead frame are bond wires. EMC challenge arises when the size of encapsulation in QFN package grows (normally  $> 5 \times 5$  mm) as the big thermal pad in lead frame and multiple narrow gaps between leads, and bond wires as well.

Figure 4. The cross section of a typical QFN package.

#### 4. CASE STUDY

#### 4.1. Simulation Models

## 4.1.1. MMIC Model

The selected MMIC is mass produced and operates at 24GHz in a tiny, high frequency device, as shown in Figure 5. The chip is packaged in a 12 pins QFN package. The size of the QFN package of the MMIC is  $2\,\mathrm{mm}$  (length)  $\times 2\,\mathrm{mm}$  (width)  $\times 0.75\,\mathrm{mm}$  (height). According to the

Figure 5. MMIC in QFN package with 12 pins (cm).

Figure 6. Simulation model of MMIC.

Table 1. Materials assignment of MMIC simulation model.

| Name          | Materials   | Permittivity | Conductivity<br>(Siemens/m) |

|---------------|-------------|--------------|-----------------------------|

| Ground Plane  | Copper      | 1            | $5.8 \times 10^{7}$         |

| PCB           | FR4 epoxy   | 4.4          | 0                           |

| Die           | GaAs        | 12.9         | 0                           |

| Encapsulation | EME-G770HCD | 4.2          | 0                           |

| Thermal Pad   | Copper      | 1            | $5.8 \times 10^{7}$         |

| Lead Frame    | Copper      | 1            | $5.8 \times 10^{7}$         |

| Bond Wire     | Copper      | 1            | $5.8 \times 10^{7}$         |

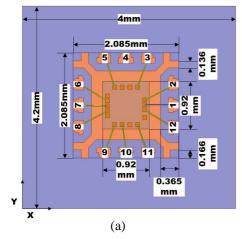

QFN package structure, the MMIC is modelled as shown in Figure 6. Key parameters of the model size are given in Figure 7.

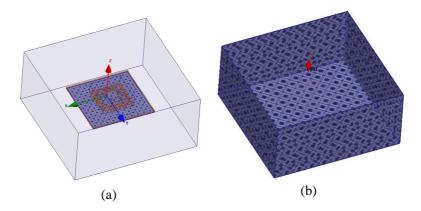

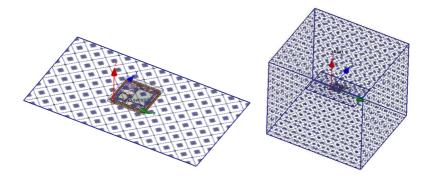

Finite conductivity boundary and radiation boundary are applied in the MMIC simulation model, as shown in Figure 8. Finite conductivity boundary means imperfect conductor which is applied

| Part Name                  | Height  |

|----------------------------|---------|

| Ground Plane               | 0.02 mm |

| PCB                        | 0.08 mm |

| Lead Frame and Thermal Pad | 0.2 mm  |

| Die                        | 0.2 mm  |

| Encapsulation              | 0.75 mm |

| (b)                        |         |

**Figure 7.** MMIC simulation model configurations. (a) Bird view and horizontal size of MMIC simulation model. (b) Vertical size of MMIC simulation model.

Figure 8. (a) Finite conductivity boundary and (b) radiation boundary applied in MMIC simulation model.

as GND of PCB. Radiation boundary is applied in the simulation of open problems where the infinite spread radiation waves need to be calculated. It is a box shape enclosure surrounding the model. In addition, 11 excitations (no excitation on lead 4 as it is not connected according to the floor plan of MMIC) are set up below the leads at Z-direction due to the electric field would be coming radiating outwards along the preceding transmission line. The materials assignment of the simulation model is described in Table 1.

## 4.1.2. RFIC Model

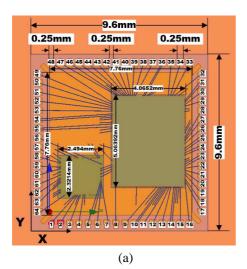

The RFIC consists of one microcontroller unit (MCU) die and one RF die using SiP technology, as shown in Figure 9. The MCU is working around 1 GHz and the RF circuit is working at  $2.4\,\mathrm{GHz}$ . The chip is packaged in a QFN package with 64 pins. Some key parameters of the model size are given in Figure 10. The size of the QFN package is  $9.6\,\mathrm{mm}$  (length)  $\times 9.6\,\mathrm{mm}$  (width)  $\times 0.75\,\mathrm{mm}$  (height). The

Figure 9. Simulation model of RFIC/SiP.

| Part Name                  | Height   |  |

|----------------------------|----------|--|

| Ground Plane               | 0.035 mm |  |

| PCB                        | 0.4 mm   |  |

| Lead Frame and Thermal Pad | 0.2 mm   |  |

| Die                        | 0.2 mm   |  |

| Encapsulation              | 0.75 mm  |  |

| (b)                        |          |  |

**Figure 10.** RFIC simulation model configurations. (a) Bird view and horizontal size of RFIC simulation model. (b) Vertical size of RFIC simulation model.

ground plane in the model is  $46.075 \,\mathrm{mm}$  (length)  $\times 26.1324 \,\mathrm{mm}$  (width)  $\times 0.035 \,\mathrm{mm}$  (height).

Similar as the MMIC model, finite conductivity boundary and radiation boundary are applied in the RFIC simulation model, as shown in Figure 11. Also, there are 64 excitations set up below the leads at Z-direction. The materials assignment to the simulation model is described in Table 2.

Figure 11. RFIC simulation model configurations.

| Name          | Materials | Permittivity | Conductivity (Siemens/m) |

|---------------|-----------|--------------|--------------------------|

| Ground Plane  | Copper    | 1            | $5.8 \times 10^{7}$      |

| PCB           | FR4 epoxy | 4.4          | 0                        |

| Die           | GaAs      | 12.9         | 0                        |

| Encapsulation | CEL9210   | 3.3          | 0                        |

| Thermal Pad   | Copper    | 1            | $5.8 \times 10^{7}$      |

| Lead Frame    | Copper    | 1            | $5.8 \times 10^{7}$      |

| Bond Wire     | Gold      | 1            | $4.1 \times 10^{7}$      |

Table 2. Materials assignment of RFIC simulation model.

## 4.2. Simulation Results

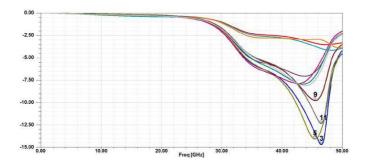

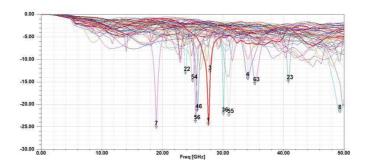

Simulations for both models are conducted under excitations with frequency swept from 0 to 50 GHz. Reflection coefficients of MMIC and RFIC model are found in Figure 12 and Figure 13. For the MMIC model, four highest reflection coefficients are highlighted regarding to different ports and frequencies as listed in Table 3. Also as listed in

Figure 12. Reflection coefficients of MMIC simulation model.

Figure 13. Reflection coefficients of RFIC simulation model.

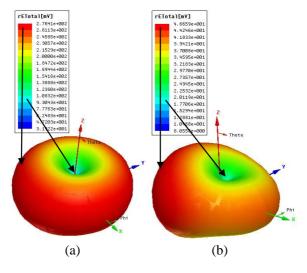

**Figure 14.** Far-field 3-D plots of RFIC simulation models. (a) MMIC at  $24\,\mathrm{GHz}$ . (b) RFIC at  $2.4\,\mathrm{GHz}$ .

| Port | Frequency           | Reflection Coefficient |

|------|---------------------|------------------------|

| 3    | $46.51\mathrm{GHz}$ | $-14.6836{\rm dB}$     |

| 5    | 45.41 GHz           | $-14.0692{\rm dB}$     |

| 9    | 45.51 GHz           | $-9.7697{\rm dB}$      |

| 11   | $46.51\mathrm{GHz}$ | $-12.3416{\rm dB}$     |

**Table 3.** Key reflection coefficients of MMIC simulation model.

Table 4, thirteen groups of highest reflection coefficients are highlighted for the RFIC. The RFIC shows more significant resonances at lower frequencies comparing to the MMIC model due to its complicate internal structure and large planar size.

Table 4. Key reflection coefficients of RFIC simulation model.

| Port | Frequency          | Reflection Coefficient |

|------|--------------------|------------------------|

| 1    | $27.6\mathrm{GHz}$ | $-24.6666\mathrm{dB}$  |

| 3    | $27.9\mathrm{GHz}$ | $-13.1154\mathrm{dB}$  |

| 4    | $34.1\mathrm{GHz}$ | $-14.4990{\rm dB}$     |

| 7    | $19\mathrm{GHz}$   | $-25.4102{\rm dB}$     |

| 8    | $49.3\mathrm{GHz}$ | $-21.8560{\rm dB}$     |

| 22   | $23.8\mathrm{GHz}$ | $-13.3182{\rm dB}$     |

| 23   | $40.8\mathrm{GHz}$ | $-15.1821{\rm dB}$     |

| 36   | $30.1\mathrm{GHz}$ | $-22.4382{\rm dB}$     |

| 46   | $25.8\mathrm{GHz}$ | $-21.6405{\rm dB}$     |

| 54   | $25\mathrm{GHz}$   | $-15.0616\mathrm{dB}$  |

| 55   | $31\mathrm{GHz}$   | $-22.7007\mathrm{dB}$  |

| 56   | $25.5\mathrm{GHz}$ | $-24.1268{\rm dB}$     |

| 63   | $35.3\mathrm{GHz}$ | $-15.6634{\rm dB}$     |

As found Figure 14, both MMIC and RFIC acts as omnidirectional antennas, that produce donut shaped radiation, under their working frequencies. The dielectric encapsulation of both models shows a good shielding effect that preventing radiation in the vertical directions. The model locates at the center and power radiated is maximum in horizontal directions from lead frames, dropping to zero directly above and below the model. It can easily affect electronic components in the surrounding area.

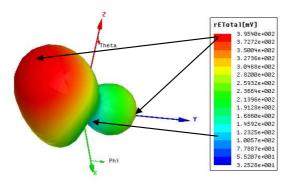

**Figure 15.** Far-field 3-D plot of MMIC simulation model at 46.51 GHz.

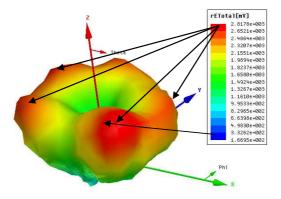

Figure 16. Far-field 3-D plot of RFIC simulation model at 19 GHz.

Figure 15 presents a far-field plot of MMIC model at  $46.51\,\mathrm{GHz}$ . It turns out a directional feature along Y axis around its resonance frequency. Also, the RFIC model shows a similar tendency at its resonance frequency. As given in Figure 16, it shows a far-field plot at  $19\,\mathrm{GHz}$ . Due to the asymmetric structure, the RFIC emits in more directions.

#### 5. CONCLUSIONS AND FUTURE WORKS

This paper presented a discussion of applying computational electromagnetics to the investigation of electromagnetic compatibility impacts of two QFN packaged ICs (MMIC and RFIC). Simulation results demonstrated that both models were acting as omnidirectional

antennas at their operating frequencies. However, directional features turned out at their resonance frequencies. Due to the asymmetric structure and internal EM environment of SiP, it emits in more directions than single packaged chip.

### ACKNOWLEDGMENT

The research work of ICs in the QFN package is financially supported by the National Natural Science Foundation of China (No. 61040032 and No. 61306134) and the Educational Industrialization Foundation of Jiangsu Province (No. JHZD10-036).

### REFERENCES

- 1. Bruns, H., C. Schuster, and H. Singer, "Numerical electromagnetic field analysis for EMC problems," *IEEE Transactions on Electromagnetic Compatibility*, Vol. 49, No. 2, 253–262, 2007.

- Ramdani, M., E. Sicard, A. Boyer, S. Ben Dhia, J. J. Whalen, T. H. Hubing, M. Coenen, and O. Wada, "The electromagnetic compatibility of integrated circuits — Past, present, and future," *IEEE Transactions on Electromagnetic Compatibility*, Vol. 51, No. 1, 78–100, 2009.

- 3. Lu, J., B. Zhu, and D. Thiel, "Full wave solution for Intel CPU with a heat sink for EMC investigations," *IEEE Transactions on Magnetics*, Vol. 46, No. 8, 3405–3408, Aug. 2010.

- 4. Zhu, B., J. Lu, and E. Li, "Electromagnetic compatibility benchmark-modelling approach for a dual-die CPU," *IEEE Transactions on Electromagnetic Compatibility*, Vol. 53, No. 1, 91–98, Feb. 2011.

- 5. Li, E., Electromagnetic Modelling and Design for 3D System Integration: 3D Integrated Circuits and Packaging, Signal Integrity, Power Integrity and EMC, Wiley-IEEE Press, 2012.

- 6. Beyne, E., "3D system integration technologies," *International Symposium on VLSI Technology, Systems and Applications*, 1–9, Apr. 2006.

- 7. Leung, L. L. W., M. L. Sham, W. Ma, Y. C. Chen, J. R. Lin, and T. Chung, "System-in-package (SiP) design: Issues, approaches and solutions," *Electronic Materials and Packaging*, 1–5, Dec. 2006.