# A Q-Band Current-Reused Low Noise Amplifier with Simultaneous Noise and Input Matching

Chun Shuang Xie<sup>1, 2</sup>, Peng Wu<sup>1</sup>, Zhong Jun Yu<sup>1, 2, \*</sup>, and Cheng Tan<sup>1</sup>

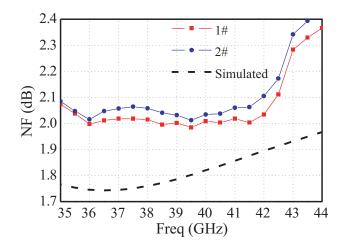

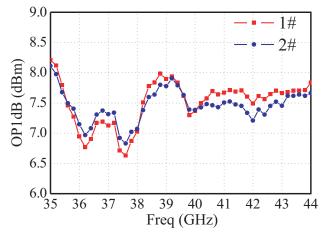

Abstract—In this paper, a Q-band GaAs low noise amplifier (LNA) for satellite communications is presented. The LNA is designed using common-source (CS) topology, self-biased configuration, and current-reused technology. Simultaneous noise and input matching are achieved by employing source series inductance. The current-reused LNA is fabricated in a 90 nm GaAs pseudomorphic high electron mobility transistor (pHEMT) process. On-wafer measurement results show that the LNA features a small-signal gain of  $23.8 \sim 24.5 \text{ dB}$ , noise figure (NF) of  $2 \sim 2.1 \text{ dB}$ , and output 1-dB compression point (OP1 dB) of  $6.6 \sim 8 \text{ dBm}$  over  $36 \sim 42 \text{ GHz}$ , while consuming 10.9 mA with a supply voltage of 5 V. The chip size is  $1.6 \times 0.8 \text{ mm}^2$  including all RF and dc pads.

### 1. INTRODUCTION

As the first stage in a receiving chain, a low noise amplifier (LNA) is one of the most critical active components in the front-end receiver of any communication system [1-4]. Since the signal received at the input of a receiver is quite weak, the common goals in designing an LNA are to achieve low noise figure (NF), reasonable gain, high linearity, as well as low power consumption, and finally to expand the dynamic range and improve the sensitivity of a receiver system [5]. Most of these performance metrics are interdependent and trade with each other, which further introduces challenges to LNAs design.

In most practical applications, the optimum supply voltage of a transistor is usually much lower than that available at the system level [6]. In traditional cases, additional DC-DC conversion stages or resistive elements are used to drop a voltage, which has the drawbacks of more complex system architecture or more power consumption. Furthermore, for systems such as modern active phased array receivers where the number of LNAs can easily reach thousands, LNA power consumption considerations may be more important [7, 8]. To alleviate this problem, current-reused structure was proposed in the literature [9–13], namely increasing circuit voltage to be equal to that provided at the system level without changing the operating point of each transistor.

The paper is organized as follows. Section 2 presents a theoretical analysis of inductive source degeneration. The detailed circuit design and implementation issues are covered in Section 3. The proposed LNA is implemented in a 90 nm GaAs process. The measurement results and comparison to state-of-the-art are presented in Section 4. Finally, Section 5 draws some conclusions.

# 2. INDUCTIVE SOURCE DEGENERATION

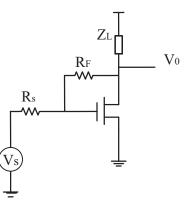

In LNA configuration, resistive feedback is often adopted to guarantee gain flatness and stability [14]. The resistive feedback is composed of a series R-L-C circuit which is connected between the gate and drain of a transistor. Unfortunately, simultaneously good input and noise matching cannot be obtained

Received 2 March 2021, Accepted 2 April 2021, Scheduled 5 April 2021

<sup>\*</sup> Corresponding author: Zhongjun Yu (yuzj@ucas.ac.cn).

<sup>&</sup>lt;sup>1</sup> Aerospace Information Research Institute, Chinese Academy of Sciences, Beijing, P. R. China. <sup>2</sup> School of Electronic, Electrical and Communication Engineering, University of Chinese Academy of Sciences, Beijing, P. R. China.

Figure 1. Schematic of a resistive feedback LNA.

with feedback configuration. To demonstrate that, let us consider a resistive feedback amplifier circuit shown in Figure 1.

The input impedance is given by

$$Z_{in} = \frac{R_F + Z_L}{1 + g_m Z_L} \tag{1}$$

Neglecting the gate and source parasitic resistance, the noise factor can be given by [15]

$$F \approx \left(1 + \frac{1}{(1 - g_m R_F)^2} \left( \left(\frac{R_F^2}{R_s}\right) \left(\frac{g_m}{2} + \frac{1}{R_F} + \frac{1}{Z_L}\right) + R_s \left(\frac{g_m}{2} + \frac{1}{Z_L} + \frac{(g_m R_F - 1)^2}{R_F}\right) \right) \right)$$

(2)

where  $R_s$  is the 50  $\Omega$  source resistance.

As shown in Eqs. (1) and (2), the noise factor and input resistance are coupled, and they both depend on  $R_F$  and  $Z_L$ . To achieve a low noise factor without scarifying input matching, inductive source degeneration was introduced to decouple the noise factor from the input impedance.

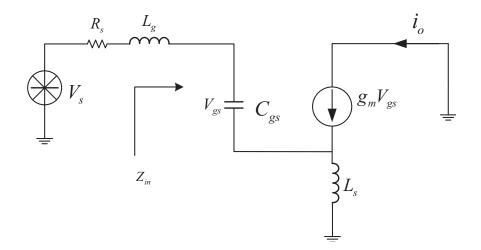

The input stage of the inductively source-degenerated CS transistor is illustrated in Figure 2. The input impedance can be given by [16]

$$Z_{in} = s(L_s + L_g) + \frac{1}{sC_{gs}} + \left(\frac{g_{m1}}{C_{gs}}\right)L_s$$

(3)

where  $L_g$  and  $L_s$  are the gate and source inductance;  $g_{m1}$  is the transconductance;  $C_{gs}$  represents the gate-source parasitic capacitor.

Figure 2. Small signal equivalent circuit for the inductively source-degenerated CS transistor.

#### Progress In Electromagnetics Research C, Vol. 111, 2021

At the series resonance of the input circuit,  $s(L_s + L_g) + \frac{1}{sC_{gs}} = 0$ . Resonance angular frequency  $\omega_0 = 1/\sqrt{C_{gs}(L_g + L_s)}$ . The input impedance is

$$Z_{in} = \left(\frac{g_{m1}}{C_{gs}}\right) L_s = \omega_T L_s \tag{4}$$

where  $\omega_T$  is the unity gain frequency of the transistor.

As shown in Eq. (4), at the resonance angular frequency, the input impedance is purely real and proportional to  $L_s$ . Good input matching can be easily obtained by choosing appropriate  $L_s$ .

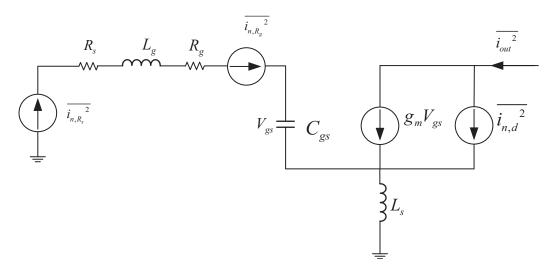

Noise factor of an LNA can be calculated by analysing the small-signal noise equivalent model, as shown in Figure 3. In the circuit,  $R_s$  is the 50  $\Omega$  source resistance,  $R_l$  the series resistance of the inductor  $L_g$ ,  $R_g$  the gate resistance of the CS transistor, and  $\overline{i_{nd}^2}$  the channel thermal noise of the transistor. Three noise sources have been considered [17]: the thermal noise of the source resistance ( $\overline{i_{n,R_s}^2}$ ), the gate-induced current noise ( $\overline{i_{n,R_l,R_g}^2}$ ), and the thermal noise of the channel current ( $\overline{i_{nd}^2}$ ).

Figure 3. Small-signal equivalent model for noise calculation.

The output noise power density arising from the channel thermal noise of the device is

$$\overline{i_{out,nd}^2} = \frac{i_{n,d}^2}{\left(1 + \frac{\omega_T L_s}{R_s}\right)^2} \tag{5}$$

The output noise power density due to the 50  $\Omega$  source is given by [18]

$$\overline{i_{n,R_s}^2} = |G_m|^2 \overline{V_{n,R_s}^2} = \left|\frac{\omega_T}{j\omega_0(R_s + \omega_T L_s)}\right|^2 \cdot 4KTR_s = \frac{4KT\omega_T^2}{\omega_0^2 R_s \left(1 + \frac{\omega_T L_s}{R_s}\right)^2} \tag{6}$$

The output noise power density due to  $R_l$  and  $R_g$  is

$$\overline{i_{n,R_l,R_g}^2} = \left|\frac{\omega_T}{j\omega_0(R_s + \omega_T L_s)}\right|^2 \cdot 4KT \left(R_l + R_g\right) = \frac{4KT \left(R_l + R_g\right)\omega_T^2}{\omega_0^2 R_s \left(1 + \frac{\omega_T L_s}{R_s}\right)^2}$$

(7)

The total output noise power density is the sum of Eqs. (5)-(7).

$$F = 1 + \frac{i_{n,R_l,R_g}^2 + i_{out,nd}^2}{i_{n,R_s}^2} = 1 + \frac{R_l + R_g}{R_s} + \gamma g_{d0} R_s \left(\frac{\omega_0}{\omega_T}\right)^2$$

(8)

where  $g_{d0}$  is the zero-bias drain conductance.

As shown in Eq. (8), the dominant term of noise factor is the last term. Moreover, for a given resonance frequency  $\omega_0$ , the noise factor improves quadratically with the transistor unity gain frequency  $\omega_T$ . As shown in Eqs. (4) and (8), noise factor and input impedance are decoupled. It is noted that simultaneously input and noise matching can be obtained by introducing source inductor  $L_s$ . In this paper, source inductances are implemented via transmission lines to achieve a compact chip area at the cost of a little more insertion loss.

# **3. CIRCUIT DESIGN**

#### 3.1. Device Size and Bias Selection

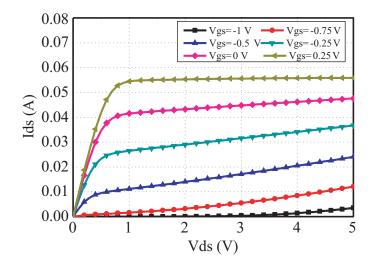

Transistor selection is the first and most important step in designing an LNA [19]. The main design targets of the proposed LNA are a gain of 22 dB and the NF below 2.5 dB in the frequency band of  $36 \sim 40$  GHz. Also, the output 1-dB compression point should be above 5 dBm. The LNA is designed using a 90 nm gate length pHEMT on a 70 µm GaAs substrate, and the cut-off frequency  $(f_T)$  and maximum oscillation frequency  $(f_{MAX})$  are 110 and 380 GHz. It includes 2 sets of metal layers, air bridges, MIM capacitors with SiN dielectric material, NiCr and GaAs resistors, and via-hole components. The minimum NF at 40 GHz is 1.39 dB. The device with four fingers and 25 µm gate width is chosen for each unit amplifying stage. The biasing point is chosen with 20% of  $I_{dss}$  to obtain noise figure and low power consumption, as shown in Figure 4. The bias point of each transistor is VDS = 1.5 V and IDS = 11 mA at VGS = -0.5 V.

Figure 4. I-V characteristics of a transistor  $(4 \times 25 \,\mu\text{m})$ .

#### 3.2. Current-Reused Configuration

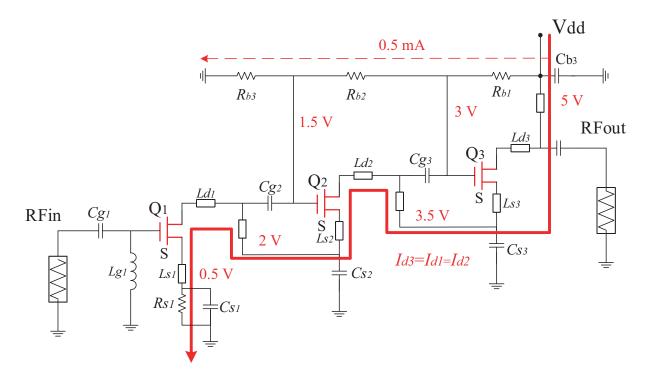

As shown in Figure 5, a current-reused configuration is utilized to guarantee lower power dissipation. The dc current flows from the drain of  $Q_3$  to the drain of  $Q_1$  by the single power supply  $V_{dd}$  which is operated at 5 V. The dc bias voltage drops from the drain of  $Q_3$  to the drain of  $Q_1$ . The amplified drain ports of  $Q_1$  and  $Q_2$  are connected to the gates of  $Q_2$  and  $Q_3$  with coupling capacitors  $C_{g2}$  and  $C_{g3}$ . The capacitors  $C_{s1}$  and  $C_{s2}$  are added for RF-bypassed paths for  $Q_1$  and  $Q_2$ , and prevent the dc current flowing into the ground. All choke inductors and by-pass capacitors are also utilized for impedance matching. All three transistors share the same dc current and operate as common-source amplifiers in a cascaded connection. The drain voltages of  $Q_3$ ,  $Q_2$ ,  $Q_1$  are operated at 5 V, 3.5 V, 2 V, respectively. The voltage between drain and source  $V_{ds}$  and the voltage between gate and source  $V_{gs}$  of each transistor are 1.5 V and -0.5 V, respectively.

Figure 5. Overall schematic of the proposed LNA.

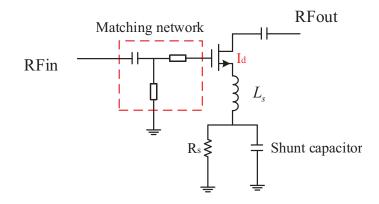

#### 3.3. Self-Bias Structure

For a depletion mode technology, negative gate voltages are required to drive the transistor working at saturate region, which brings inconvenience in the application. A self-biased topology [20] was proposed by inserting a parallel RC structure between the source inductor and ground, as shown in Figure 6. The resistor, in which drain current flows, was sized to provide the selected positive dc voltages at the source terminal. Thus, fixing to zero the voltage at the gate terminal with a dc path to the ground, any required negative gate-source voltage  $V_{qs}$  could be obtained. It is expressed as follows:

$$V_{gs} = V_g - V_s = -V_s = -I_d R_s \tag{9}$$

Moreover, a shunt capacitor was used to provide a direct path to the ground to the RF signal, reducing the detrimental effects of the resistors on gain and noise performance.

Figure 6. Self-bias structure of a transistor.

#### 4. MEASUREMENT RESULTS

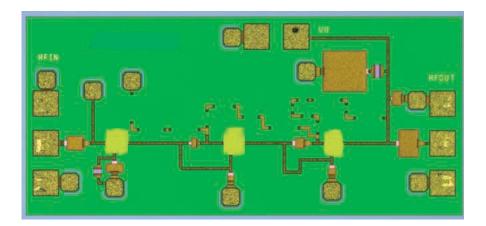

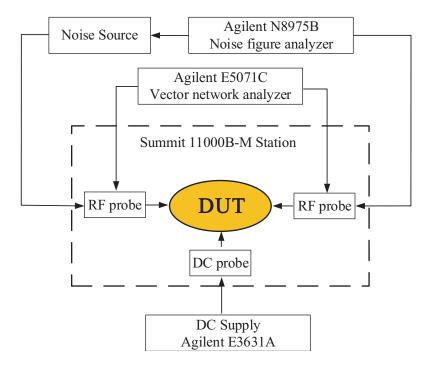

The proposed Q-band LNA is fabricated in a 90 nm GaAs pHEMT process with 70  $\mu$ m substrate thickness. Figure 7 shows a micrograph of the LNA with a compact  $1.6 \times 0.8 \text{ mm}^2$  chip size, including all RF and dc pads. The LNA is measured by on-wafer probing at RF and dc pads. The measurement setup is shown in Figure 8. The LNA is measured by the Cascade Microtech probe station, Summit 11000B-M. *S* parameters are measured on-wafer by Agilent E5071C network analyzer, and the noise figure is measured on-wafer by Agilent N8975B noise figure analyzer.

Figure 7. Micrograph of the proposed LNA.

Figure 8. Measurement setup (S-parameter and noise figure).

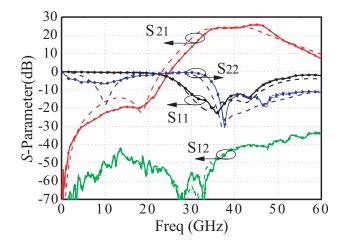

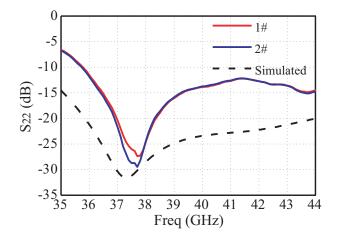

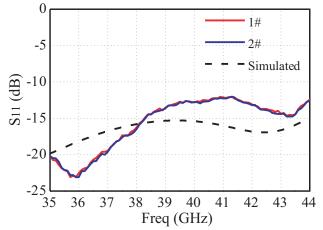

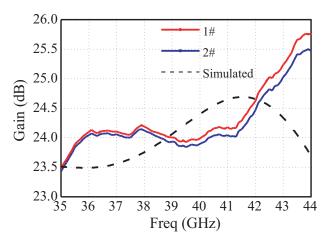

For arbitrary 2 sites (1# and 2#) measured across the wafer, the measured and simulated Sparameters, NFs, and OP1 dB of the proposed LNA are depicted from Figure 9 to Figure 14. As shown in Figures 9, we can see that the measured S-parameter curves of 1# and 2# almost overlap, which indicates that the GaAs process is stable and consistent. As shown in Figures  $10\sim13$ , the LNA achieves

**Figure 9.** Measured (solid line) and simulated (dashed line) *S*-parameters of the proposed LNA (0–60 GHz).

Figure 11. Measured and simulated  $S_{22}$  of the proposed LNA.

Figure 10. Measured and simulated  $S_{11}$  of the proposed LNA.

Figure 12. Measured and simulated gain of the proposed LNA.

a flat small-signal gain of  $23.8 \sim 24.5 \,\mathrm{dB}$  at frequency band of  $36 \sim 42 \,\mathrm{GHz}$ , and the NF is in the range of  $2 \sim 2.1 \,\mathrm{dB}$ . Input and output return-loss is better than 10 dB. The measured results exhibit a frequency shift about 1 GHz in operating frequency bands compared with the simulated results, which is mainly caused by the improper modeling of the process and the high sensitivity of some matching networks. Noise figure measurement result is approximately 0.2 dB higher than simulated results.

As shown in Figure 14, the measured OP1dB from 36–42 GHz is  $6.6 \sim 8 \,\mathrm{dBm}$ .

The performance of LNA can be assessed by the figure of merit (FOM) related to gain, bandwidth, OP1 dB, noise figure, and dc consumption. The definition of FOM can be written by [21]:

$$FOM = \frac{Gain \,[\text{abs}] \cdot OP1 \,[\text{mW}] \cdot Bandwidth \,[\text{GHz}]}{P_{DC} \,[\text{mW}] \cdot (NF - 1) \,[\text{abs}]}$$

(10)

Table 1 compares the performance of the proposed LNA with other state-of-the-art LNAs. Compared with other works, the proposed LNA exhibits a good trade-off among gain, noise figure, and dc power consumption.

Figure 13. Measured and simulated NF of the proposed LNA.

Figure 14. Measured OP1dB of the proposed LNA.

| Ref.         | Freq<br>(GHz) | NF<br>(dB) | Gain<br>(dB) | OP1<br>(dBm) | PDC<br>(mW) | Area $(mm^2)$ | FOM  | Tech                              |

|--------------|---------------|------------|--------------|--------------|-------------|---------------|------|-----------------------------------|

| [22]         | 26-32         | 1.8-2.2    | 12.4         | 1.4          | 98          | 0.7           | 0.69 | $0.25\mu\mathrm{m~SiGe}$          |

| [23]         | 35 - 50       | 3.8 - 5    | 23           | /            | 62.6        | 3             | /    | $0.15\mu\mathrm{m}~\mathrm{GaAs}$ |

| [24]         | 29-37         | 3.1 - 4.1  | 25.5 - 28.5  | 5.3          | 80          | 0.21          | 6.48 | $0.25\mu\mathrm{m}~\mathrm{SiGe}$ |

| [25]         | 27 - 31.5     | 1.7        | 16 - 18      | 3            | 115         | 3.6           | 1.02 | $70\mathrm{nm}~\mathrm{GaAs}$     |

| [26]         | 35 - 50       | 2.5 - 3    | 25 - 28      | 9.6          | 155         | 1.62          | 15.8 | $0.1\mu\mathrm{m}~\mathrm{GaAs}$  |

| [27]         | 33-41         | 3-4        | 15           | 13           | 280         | 0.7           | 21   | $0.12\mu\mathrm{m~GaN}$           |

| This<br>work | 36–42         | 2 - 2.1    | 23.8 - 24.5  | 6.6–8        | 54.5        | 1.28          | 19.9 | 90 nm GaAs                        |

Table 1. Comparison with similar works in literature.

# 5. CONCLUSION

A current-reused LNA for Q-band satellite communications application has been presented. The three cascaded common-source amplifying stages share the same current. Source series inductance has been employed to obtain simultaneous noise and input match. The proposed LNA is implemented in a 90 nm GaAs pHEMT technology. The chip area including RF and dc pads is  $1.6 \times 0.8 \text{ mm}^2$ . The measurement results show a small-signal gain of  $23.8 \sim 24.5 \text{ dB}$ , noise figure (NF) of  $2 \sim 2.1 \text{ dB}$ , and output 1-dB compression point (OP1dB) of  $6.6 \sim 8 \text{ dBm}$  over  $36 \sim 42 \text{ GHz}$ , while consuming 10.9 mA from a 5 V voltage supply. A high FOM of 19.9 has been achieved.

# REFERENCES

- Hu, J., K. Ma, S. Mou and F. Meng, "A seven-octave broadband LNA MMIC using bandwidth extension techniques and improved active load," *IEEE Trans. Circuits Syst. I, Reg. Papers*, Vol. 65, No. 10, 3150–3161, Oct. 2018.

- Varonen, M., et al., "An MMIC low-noise amplifier design technique," *IEEE Trans. Microw. Theory Techn.*, Vol. 64, No. 3, 826–835, Mar. 2016.

#### Progress In Electromagnetics Research C, Vol. 111, 2021

- Sarkar, M., P. Banerjee, and A. Majumder, "Design of broadband MMIC low noise amplifier at W band using GaAs pHEMTs," 2017 International Conference on Innovations in Electronics, Signal Processing and Communication (IESC), 194–198, Shillong, 2017.

- Khan, M., et al., "Ka-band GaAs MMIC LNA using a 0.15 μm metamorphic InGaAs," 2016 IEEE MTT-S International Wireless Symposium (IWS), 1–4, Shanghai, China, 2016.

- Moezzi, M. and M. Sharif Bakhtiar, "Wideband LNA using active inductor with multiple feedforward noise reduction paths," *IEEE Trans. Microw. Theory Techn.*, Vol. 60, No. 4, 1069–1078, Apr. 2012.

- Colangeli, S., W. Ciccognani, M. Vittori, M. Palomba, and E. Limiti, "A novel current-reuse architecture demonstrated on a two-stage GaN-on-SiC LNA," 2017 IEEE Asia Pacific Microwave Conference (APMC), 634–637, Kuala Lumpar, 2017.

- 7. Jussila, J. and P. Sivonen, "A 1.2-V highly linear balanced noise-cancelling LNA in 0.13-μm CMOS," *IEEE J. Solid-State Circuits*, Vol. 43, No. 3, 579–587, Mar. 2008.

- Uzunkol, M. and G. M. Rebeiz, "A 65 GHz LNA/phase shifter with 4.3 dB NF using 45 nm CMOS SOI," *IEEE Microw. Wireless Compon. Lett.*, Vol. 22, No. 10, 530–532, Oct. 2012.

- 9. Khoshroo, P., M. Elmi, and H. M. Naimi, "A low-power current-reuse resistive-feedback LNA in 90 nm CMOS," 2016 24th Iranian Conf on Electrical Engineering (ICEE), 917–920, Shiraz, 2016.

- Kong, S., H. D. Lee, M. Lee, and B. Park, "A V-band current-reused LNA with a doubletransformer-coupling technique," *IEEE Microw. Wireless Compon. Lett.*, Vol. 26, No. 11, 942–944, Nov. 2016.

- 11. Hsieh, H. and L. Lu, "Design of ultra-low-voltage RF frontends with complementary current-reused architectures," *IEEE Trans. Microw. Theory Tech.*, Vol. 55, No. 7, 1445–1458, Jul. 2007.

- Noh, N. M., A. Hashim, K. Y. Tan, and Y. Y. Tan, "Design and analysis of the current reuse technique and folded cascode power con-strained simultaneous noise and input matching LNAs with distributed and lumped parasitic," 2010 IEEE Asia Pacific Conf on Circuits and Systems, 292–295, Kuala Lumpur, 2010.

- 13. Yang, C., W. Hsieh, and Y. Chiang, "A fully integrated and high linearity UWB LNA implemented with current-reused technique and using single-biasing voltage," 2007 European Conf on Wireless Technologies, 94–97, Munich, 2007.

- Hu, J. and K. Ma, "A 0.1–52-GHz triple cascode amplifier with resistive feedback," *IEEE Microw. Wireless Compon. Lett.*, Vol. 29, No. 8, 538–540, Aug. 2019.

- Ismail, A. and A. A. Abidi, "A 3–10-GHz low-noise amplifier with wideband LC-ladder matching network," *IEEE J. Solid-State Circuits*, Vol. 39, No. 12, 2269–2277, Dec. 2004.

- Meng, C. and Y. Hsiao, "Design optimization of inductively source-degenerated FET LNAs using noise transformation matrix (invited talk)," 2016 IEEE International Symposium on Radio-Frequency Integration Technology (RFIT), 1–3, Taipei, Taiwan, 2016.

- Ma, P., M. Racanelli, J. Zheng, and M. Knight, "A novel bipolar-MOSFET low-noise amplifier (BiFET LNA), circuit configuration, design methodology, and chip implementation," *IEEE Transactions on Microwave Theory and Techniques*, Vol. 51, No. 11, 2175–2180, Nov. 2003.

- Shaeffer, D. K. and T. H. Lee, "A 1.5-V, 1.5-GHz CMOS low noise amplifier," *IEEE J. Solid-State Circuits*, Vol. 32, No. 5, 745–759, May 1997.

- Nikandish, G. and A. Medi, "Transformer-feedback interstage bandwidth enhancement for MMIC multistage amplifiers," *IEEE Trans. Microw. Theory Tech.*, Vol. 63, No. 2, 441–448, Feb. 2015.

- Feng, C., X. P. Yu, W. M. Lim, and K. S. Yeo, "A compact 2.1–39 GHz self-biased low-noise amplifier in 65 nm CMOS technology," *IEEE Microw. Wireless Compon. Lett.*, Vol. 23, No. 12, 662–664, Dec. 2013.

- Wei, M. D., S. F. Chang, and R. Negra, "Triple cascaded current-reuse low noise amplifier," Analog Integr. Circ. Sig. Process., Vol. 80, 327–333, 2014.

- Xie, H., Y. J. Cheng, and Y. Fan, "A K-band high interference-rejection GaAs low-noise amplifier using multizero control method for satellite communication," *IEEE Microw. Wireless Compon. Lett.*, Vol. 30, No. 11, 1069–1072, Nov. 2020.

- 23. Parveg, D., M. Varonen, and M. Kantanen, "A full Ka-band GaN-on-Si low-noise amplifier," 2020 50th EuMC, 1015–1018, Utrecht, Netherlands, 2021.

- 24. Chen, Z., H. Gao, D. Leenaerts, D. Milosevic, and P. Baltus, "A 29–37 GHz BiCMOS low-noise amplifier with 28.5 dB peak gain and 3.1–4.1 dB NF," *2018 IEEE RFIC*, 288–291, Philadelphia, PA, USA, 2018.

- Polli, G., et al., "Ka-/V-band self-biased LNAs in 70 nm GaAs/InGaAs technology," 2018 14th PRIME, 197–200, Prague, Czech Republic, 2018.

- Wang, Z., et al., "A Q-band self-biased LNA in 0.1-μm GaAs pHEMT technology," 2019 12th UCMMT, 1–4, London, United Kingdom, 2019.

- Park, J., et al., "A Ka-band low noise amplifier in 0.15 μm GaAs E-mode pHEMT technology," 2018 ISOCC, 255–256, Daegu, Korea (South), 2018.