# Inverse-Designed Metamaterials for On-Chip Combinational Optical Logic Circuit

Qingze Tan<sup>1, 2, 3, 4</sup>, Chao Qian<sup>1, 2, 3, 4, \*</sup>, and Hongsheng Chen<sup>1, 2, 3, 4, \*</sup>

Abstract—Optical analog computing has recently sparked growing interest due to the appealing characteristics of low energy consumption parallel processing and ultrafast speed, spawning it complementary to conventional electronic computing. As the basic computing unit, optical logic operation plays a pivotal role for integrated photonics. However, the reported optical logic operations are volumetric and single-functional, which considerably hinders the practical cascadability and complex computing requirement. Here, we propose an on-chip combinational optical logic circuit using inverse design. By precisely engineering the scattering matrix of each small-footprint logic gate, all basic optical logic gates (OR, XOR, NOT, AND, XNOR, NAND, and NOR) are realized. On this foundation, we explore the assembly of these basic logic gates for general purpose combinational logic circuits, including optical half-adder and code converter. Our work provides a path for the development of integrated, miniaturized, and cascadable photonic processor for future optical computing technologies.

### 1. INTRODUCTION

With the increasing volume of information generated every day, the existing electronic computers have become increasingly difficult to meet the requirement of processing data with high speed and efficient energy. The dilemma of electronic computers mainly stems from the interconnect delay and large heat generation. Optical analogy computing, taking photons as the information carriers instead of electrons, heralds a superior alternative in information processing [1]. Due to its unique characteristics of processing data with light speed, low energy consumption, and massive parallel processing ability, optical computing has great potential in a host of practical scenarios, including autonomous driving and augmented reality, which involves high-throughput and low-latency data processing [2, 3]. In this respect, optical computing composed by integrated optical circuit promises to be complementary to the digital counterpart. As the basic computing element, optical logic gates are of particular importance to realize a general-purpose integrated optical circuit. It has been attracting substantial attention to achieve a small-footprint and cascadable optical logic gate [4].

Metamaterials, as artificial composite materials with engineered atoms, offer a versatile platform to enable a myriad of functional optical computing components [5–29]. Recent examples include equationsolver [30], spatial differentiation [31], and optical neural network [32]. Previous designs about optical logic gate have centered on two routes: linear or nonlinear interference effect, embodied as free-space and on-chip appearances. For nonlinear optical logic gates, they typically necessitate high signal powers and large interaction lengths, because the optical nonlinearities of natural materials are relatively weak [33, 34]. For linear optical logic gates, a variety of logic gates have been demonstrated using

Received 15 September 2022, Accepted 7 December 2022, Scheduled 14 December 2022

<sup>\*</sup> Corresponding author: Chao Qian (chaoq@intl.zju.edu.cn), Hongsheng Chen (hansomchen@zju.edu.cn).

<sup>&</sup>lt;sup>1</sup> ZJU-UIUC Institute, Interdisciplinary Center for Quantum Information, State Key Laboratory of Extreme Photonics and Instrumentation, Zhejiang University, Hangzhou 310027, China. <sup>2</sup> ZJU-Hangzhou Global Science and Technology Innovation Center, Key Lab. of Advanced Micro/Nano Electronic Devices & Smart Systems of Zhejiang, Zhejiang University, Hangzhou 310027, China. <sup>3</sup> Jinhua Institute of Zhejiang University, Zhejiang University, Jinhua 321099, China. <sup>4</sup> Shaoxing Institute of Zhejiang University, Zhejiang University, Shaoxing 312000, China.

photonic crystals nanowire networks and metasurfaces [35–47]. Previous studies mainly focus on the implementation of individual logic gate, while the combinational logic circuit has not yet been extensively studied. Furthermore, most optical logic gates rely on the constructive or destructive interferences within three-dimensional volume, making their integration and miniaturization very difficult. It is thus highly desirable to achieve a cascadable and small-footprint logic gate that provides sufficient levels of cascadability and meets user-defined demand for a variety of combinational optical logic circuits [4].

In this work, we propose an on-chip combinational optical logic circuit composed of different logic gates. Each logic gate is physically constructed by a small-footprint inhomogeneous metamaterial. By inversely designing the spatial metamaterial layout, the scattering matrix of the logic gate can be arbitrarily engineered to mimic the behavior of logic operation. The logic gate is strongly optimized using topology optimization algorithm, whose average element error (AEE) is reduced to  $10^{-5}$ . Both output amplitude and phase of the logic gate can be accurately controlled. We realize all basic optical logic gates (OR, XOR, NOT, AND, XNOR, NAND, and NOR) as the fundamental building block for optical combinational logic circuit. Furthermore, we explore the cascadability of logic gate to facilitate optical half-adder and code converter. This universal design strategy has the potential to enable compact and cascadable photonic processors for general purposes.

## 2. RESULTS

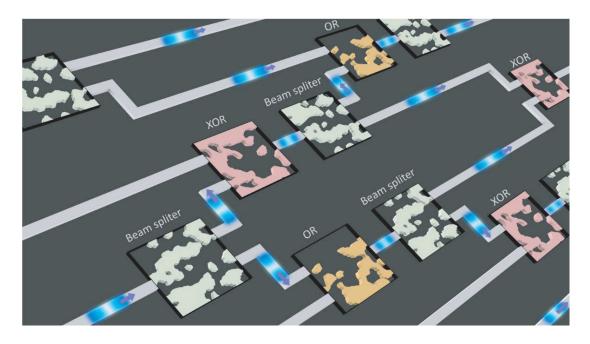

A single optical logic gate only has fixed and limited functionality. To enable a flexible and complex functionality, it is highly anticipated to assemble different optical logic gates, analogous to electronic circuit. Fig. 1 shows the schematic diagram of the combinational optical logic circuit. The geometry and metamaterial layout of each logic gate should be carefully designed. As shown in Fig. 2(a), the physical geometry of the logic gate consists of a two-dimensional (2D) domain sandwiched by planar metallic waveguides. The top and bottom parts are electromagnetic (EM) absorber. We consider the fundamental TE10 mode to carry information operating at f = 5 GHz (the working wavelength  $\lambda = 6 \text{ cm}$ ). Two inputs (rectangular waveguides, port 1 and port 2) and one output (port 3) are attached on the left and right sides, so the transmission matrix of the logical gate can be described

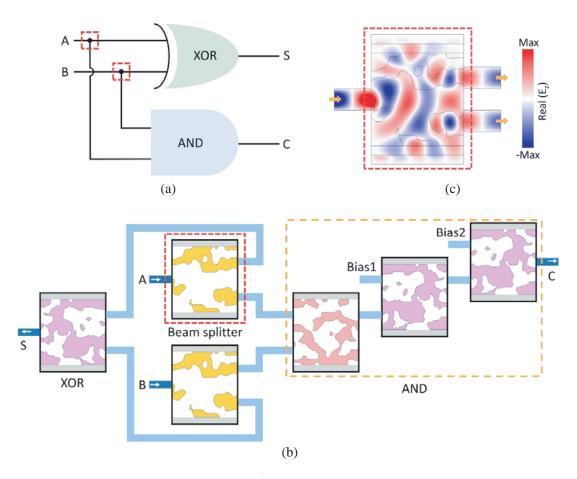

**Figure 1.** Schematic of the combinational optical logic circuit. Each optical logic gate is inversely designed with topology optimization to mimic the behavior of electronic logic gate. Different optical logic gates are physically assembled in a certain rule to build up a combinational logic circuit for user-defined functionality.

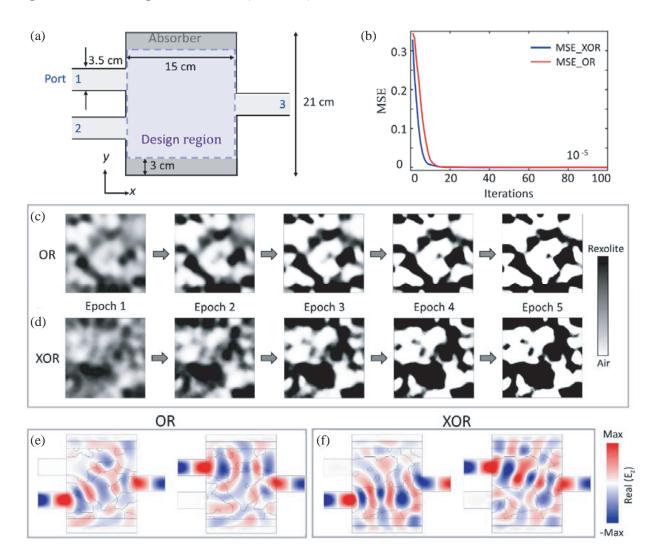

**Figure 2.** Design of the optical logic gate. (a) The physical geometry of optical logic gate. It contains two input ports and one output port on either side of the design region, which is surrounded by absorption boundary on top and bottom. The inverse design aims to find the needed material distribution in the design region. (b) The AEE over iterations. (c), (d) Time-evolution of the material density of (c) OR gate and (d) XOR gate. (e), (f) The simulation results of electric field distribution with different input modes of (e) OR gate and (f) XOR gate.

as a  $2 \times 1$  matrix  $\begin{pmatrix} S_{31} \\ S_{32} \end{pmatrix}$ . In addition, there is a  $2 \times 2$  reflection matrix  $\begin{pmatrix} S_{11} & S_{12} \\ S_{21} & S_{22} \end{pmatrix}$ , which shall be miniaturized to near zero. The central purple highlighted region is the design region  $(15 \text{ cm} \times 15 \text{ cm}, 2.5\lambda \times 2.5\lambda)$ , where the dielectric distribution associated with the expected scattering matrix needs to be found during the optimized procedure.

The EM optimization that finds the dielectric distribution associated with the scattering matrix of the logical gate is undertaken using topological optimization method [48]. Comparatively, deep learning enabled inverse design always needs to discretize the design region into a number of fixed elements, such as circular and square ones, and the ultimate optimized result is generated from a combination of these pixels [49, 50]. With the increase in the number of degrees of freedom, the solution space increases exponentially, leading to the burdensome task of large dataset collection and complex algorithm modeling. Topology optimization can obtain the optimal dielectric distribution without constraint on the geometry and huge cost on data collection. In our work, we adopt the density-based method to inversely design the dielectric distribution of the logic gate. The design domain is discretized into arbitrarily shaped N elements, which is different from the pixel design region. A random initial density distribution is given inside the design region. To facilitate the topology optimization, we deploy a loss function AEE defined as the complex-plane "distance" between the S parameters and their expected values. Evidently, for OR logic gate, the transmission matrix is set as to  $S_{32}$ aensure the output phases are identical with different input modes. The identical amplitudes of  $S_{31}$ and  $S_{32}$  lay the foundation for the following cascaded circuit. For XOR logic gate, the transmission  $\begin{vmatrix} S_{31} \\ S_{32} \end{vmatrix} =$  $\begin{vmatrix} a \\ -a \end{vmatrix}$ . This results in zero output field when the two input matrix is correspondingly set as ports are excited simultaneously, which is analogous to the characteristics of XOR logic gate. The optimization goal is to minimize the AEE of logic gate. The optimization variable is defined by the relative permittivity at each spatial point in the design region, which is bounded between air with the relative permittivity of 1 and Resolite, a low-loss polystyrene with the relative permittivity of 2.53. After dozens of iterations, convergence is obtained, and the AEE is decreased to  $10^{-5}$ , indicating that the OR and XOR logic gates can implement the target matrix with negligible errors (Fig. 2(b)). Having a satisfactory convergence, the next optimization step is performed using penalty function to enforce the relative permittivity binarized as air or Rexolite. The iterative process of binaryzation is displayed in Figs. 2(c), (d), where each epoch contains 100 iterations. We stop the optimization process when the error in the binarized structure is satisfactory. Finally, we obtain the dielectric distribution that almost only contains two materials, without intermediate value, which is friendly for practical fabrication. The 0.6850.685transmission matrices of OR and XOR logic gates are , respectively, and the and 0.685-0.685reflection matrices of these two logic gates are almost zero. The electric field distributions of the optical

OR and XOR logic gates with different input modes are plotted in Figs. 2(e), (f). For OR logic gate (Fig. 2(e)), the output amplitudes and phases under different input excitations are identical. For XOR

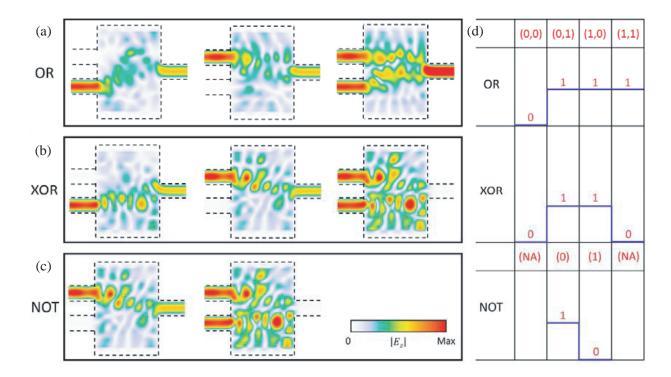

**Figure 3.** Result of the optical OR, XOR and NOT logic gates. (a), (b), (c) The electric magnitude distribution of (a) OR gate, (b) XOR gate, and (c) NOT gate with different input modes. (d) The truth table of the proposed optical OR, XOR, and NOT gates.

logic gate (Fig. 2(e)), the amplitudes are the same while the output phases are opposite under different input excitations. In addition, we can see that there are almost no reflection waves inside OR and XOR logic gates, which is crucial for cascaded photonic system. The electric field distributions of optical OR and XOR gates are well matched with the target scattering matrices.

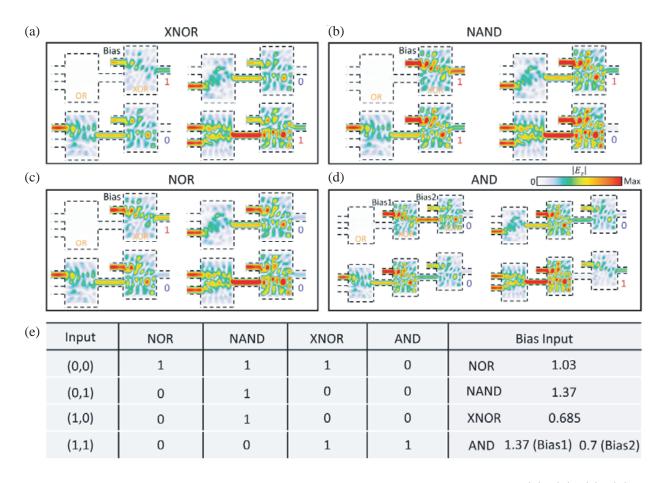

Figures 3(a), (b), (c) show the simulation results of the electric field magnitude  $(|E_z|)$  with different input modes. All simulation results are consistent with the target results. If we employ one input port of XOR logic gate as a bias input, it behaves as NOT gate, as presented in Fig. 3(c). Fig. 3(d) shows the truth table of the optical OR, XOR and NOT gates. Other optical logic gates can be achieved by cascading these OR, XOR, NOT logic gates with a certain rule. Fig. 4 shows the simulation results of XNOR, NAND, NOR and AND logic gates, implemented by cascaded photonic element. For the design of XNOR, we cascade OR and XOR and set bias input with the field amplitude being 0.685 times input amplitude. The output field is zero when only one input port is activated. As for the other two cases, the output field is nonzero, meaning that the XNOR gate is realized, as shown in Fig. 4(a) For the design of NAND gate, we cascade OR and XOR and set bias input with the field amplitude being 1.37 times input amplitude. Only when all input ports are excited the output field is zero, as shown in Fig. 4(b). For the design of NOR gate, we cascade OR and XOR and set bias input with the field amplitude being 1.03 times input amplitude. In particular, when both input ports are activated, only the electric fields from the bias input contributes to the output power. For other three cases, the output power is significantly reduced as shown in Fig. 4(c). The ratio of output power between the

**Figure 4.** Results of the optical XNOR, NAND, NOR, and AND logic gates. (a), (b), (c), (d) The electric magnitude distribution of (a) XNOR gate, (b) NAND gate, (c) NOR gate, and (d) AND gate with different input modes. These logic gates are designed with two- or three-level cascaded structure, by adding a permanent bias channel. (e) The truth table of the proposed optical XNOR, NAND, NOR and AND gate. The values of needed bias inputs are listed for different optical logic gates.

output states 1 and 0 is up to 9 : 1. For the design of AND gate, we cascade one OR and two XOR and set bias1 input with the field amplitude being 1.37 times and bias2 input with the field amplitude being 0.7 times input amplitude, as shown in Fig. 4(d). Similar to NOR gate, the output power of logic state 1 is almost 9 times that of logic state 0. Fig. 4(e) presents the truth table of the proposed optical XNOR, NAND, NOR and AND gate, and the values of needed bias inputs corresponding to different optical logic gates.

We then progress to the design of optical half adder as the first demonstration of optical combinational logic circuit. Fig. 5(a) exhibits conventional digital logic circuit of half adder, which is composed of AND and XOR gates. The parallel connection is marked by red dotted box in Fig. 5(a). We innovatively replace it with the beam splitter achieved by the designed photonic structure shown in Fig. 5(c). The two outputs have the identical phase with different inputs, and their amplitudes are the same which is half of the input magnitude. Such characteristics make the proposed beam splitter a useful tool in combinational logic circuit. Based on this, Fig. 5(b) shows the optical half adder where ports A and B are the input ports, and ports C and S are carry bit and sequence bit, respectively. The proposed optical half adder has an excellent agreement with conventional digital combinational circuit. Fig. 6 shows the simulation results of the optical half adder under four different input cases ((a) A = 0, B = 0; (b) A = 0, B = 1; (c) A = 1, B = 0; (d) A = 1, B = 1). We can see that the truth value of carry bit is 1 only when two ports are both turned on. The simulated results demonstrate that the optical half adder coincides with the truth value of digital half adder.

**Figure 5.** Design of the optical half adder. (a) The architecture of conventional digital half adder, which is composed of AND and XOR gates. (b) The optical half adder. A and B are the input ports, and C and S are carry bit and sequence bit, respectively. The inputs from A and B ports are split into two by a beam splitter and then simultaneously pass through AND and XOR gate. (c) The simulation result of the beam splitter. The output phase and amplitude at two output ports are exactly the same.

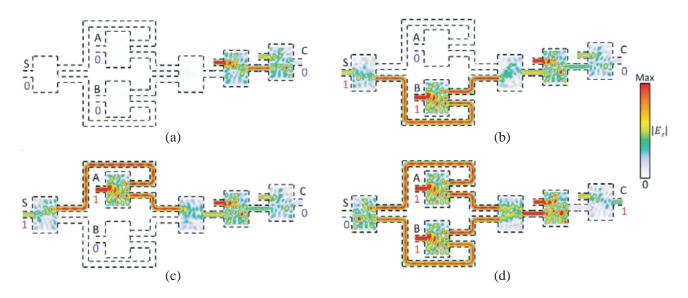

Figure 6. Results of the optical half adder. The electric magnitude distribution of the optical half adder with four different input modes (a) A = 0, B = 0, (b) A = 0, B = 1, (c) A = 1, B = 0 and (d) A = 1, B = 1.

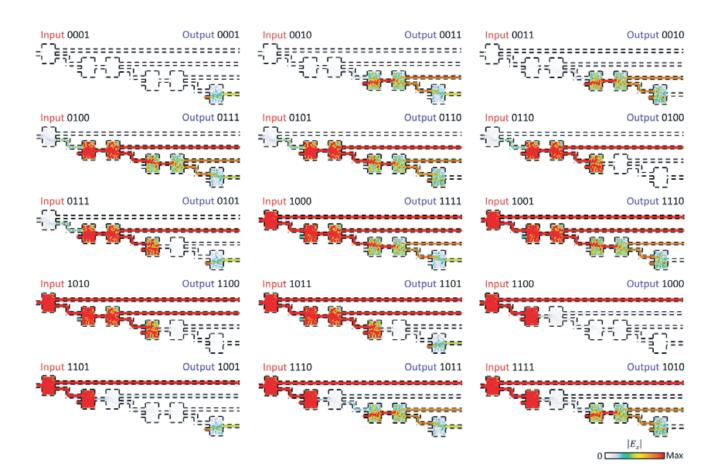

In order to further benchmark the optical combinational logic circuit, we design a code converter to convert four bit Gray code to four bit natural binary code. The truth value table of such a converter is listed in Fig. 7(a). According to the truth table, we design the corresponding optical combinational logic circuit composed of connected beam splitters and XOR gates, as shown in Fig. 7(b). The four input ports are G3, G2, G1, and G0, and the output ports are B3, B2, B1, and B0. Fig. 8 shows the simulation results of the electric field magnitude with 15 different input modes (except the input case of 0000). We regard the truth value as 0 when the output fields are almost zero. Otherwise, the truth value is 1. From the simulation results, the proposed optical code converter has a good agreement with the truth value table in Fig. 7(a). It should be noted that the values of four inputs from G0 to G3 are increased (G0 = 1, G1 = 2.9, G2 = 8.5, G3 = 17) due to the utilization of beam splitters. The output fields are nearly zero when the truth value is 0, because the S parameters of optical logic gate are strongly optimized to make the error negligible.

| Gray code<br>G <sub>3</sub> G <sub>2</sub> G <sub>1</sub> G <sub>0</sub> | Natural binary code<br>B <sub>3</sub> B <sub>2</sub> B <sub>1</sub> B <sub>0</sub> | Gray code<br>G <sub>3</sub> G <sub>2</sub> G <sub>1</sub> G <sub>0</sub> | Natural binary code<br>B <sub>3</sub> B <sub>2</sub> B <sub>1</sub> B <sub>0</sub> |

|--------------------------------------------------------------------------|------------------------------------------------------------------------------------|--------------------------------------------------------------------------|------------------------------------------------------------------------------------|

|                                                                          |                                                                                    |                                                                          |                                                                                    |

| 0001                                                                     | 0001                                                                               | 1101                                                                     | 1001                                                                               |

| 0011                                                                     | 0010                                                                               | 1111                                                                     | 1010                                                                               |

| 0010                                                                     | 0011                                                                               | 1110                                                                     | 1011                                                                               |

| 0110                                                                     | 0100                                                                               | 1010                                                                     | 1100                                                                               |

| 0111                                                                     | 0101                                                                               | 1011                                                                     | 1101                                                                               |

| 0101                                                                     | 0110                                                                               | 1001                                                                     | 1110                                                                               |

| 0100                                                                     | 0111                                                                               | 1000                                                                     | 1111                                                                               |

B3

B2

**B**1

(b) **Go BO Figure 7.** Design of the optical code converter. (a) The truth value table of the code converter that transforms four bit Gray code to four bit natural binary code. (b) The optical implementation of code

converter. The four input ports are G3, G2, G1, and G0, and the output ports are B3, B2, B1, and B0.

G11

Figure 8. Results of the optical code converter. All the results are consistent with the expectation. For the case of input 0000, the output is certainly 0000 (not shown).

G3

Beam splitter

G2

XOR

### 3. CONCLUSION

In conclusion, we proposed an on-chip combinational optical logic circuit assembled of different logical

gates. The optical logical gate is inversely designed to make the scattering matrix identical to the logical operation, utilizing topology optimization to obtain the metamaterial profile. We imposed a realistic dielectric parameter to logical gate to ensure that they are friendly for practical fabrication. We demonstrated all kinds of basic optical logic gates, OR, XOR, NOT, AND, XNOR, NAND, and NOR with high contrast ratios, some of which must be realized by adding a bias channel to ensure, such as '0 NOR 0 = 1' and '0 NAND 0 = 1'. The involvement of bias channel is also helpful for loss compensation in an optical cascaded system. We cascaded these logic gates in a certain rule to build upcom binational logic circuit, including optical half-adder and code converter. Beyond that, other functional optical circuit can be readily achieved with a more sophisticated network based on the designed optical logic gates. Although the designed logic gate was demonstrated in the microwave, the concept is relevant and can be readily generalized to higher frequencies with a similar framework. These findings will lead to various optical logic modules and benefit dense on-chip integration applications. Alongside, the inverse-designed metamaterials provide a flexible platform for precise manipulation of EM waves and multichannel data processing.

### ACKNOWLEDGMENT

This work at Zhejiang University was sponsored by the National Natural Science Foundation of China (NNSFC) under grant Nos. 62101485, 61625502, 11961141010, and 61975176, the Top-Notch Young Talents Program of China, and the Fundamental Research Funds for the Central Universities.

### REFERENCES

- 1. Caulfield, H. J. and S. Dolev, "Why future supercomputing requires optics," Nat. Photon., Vol. 4, 261-263, 2010.

- 2. Silva, A., F. Monticone, G. Cadtaldi, V. Galdi, A. Alu, and N. Engheta, "Performing mathematical operations with metamaterials," Science, Vol. 343, 160–163, 2014.

- 3. Zhou, H., J. Dong, J. Cheng, W. Dong, C. Huang, Y. Shen, Q. Zhang, M. Gu, C. Qian, H. Chen, Z. Ruan, and X. Zhang, "Photonic matrix multiplication lights up photonic accelerator and beyond," Light: Sci. Appl., Vol. 11, 30, 2022.

- 4. Miller, D. A. B., "Are optical transistors the logical next step?" Nat. Photon., Vol. 4, 3–5, 2010.

- Urbas, A. M., Z. Jacob, L. D. Negro, N. Engheta, A. D. Boardman, P. Egan, et al., "Roadmap on 5.optical metamaterials," J. Opt., Vol. 18, 093005, 2016.

- 6. Qian, C., X. Lin, Y. Yang, X. Xiong, H. Wang, E. Li, I. Kaminer, B. Zhang, and H. Chen, "Experimental observation of superscattering," Phy. Rev. Lett., Vol. 122, 063901, 2019.

- 7. Qian, C., B. Zheng, Y. Shen, L. Jing, E. Li, L. Shen, and H. Chen, "Deep-learning-enabled selfadaptive microwave cloak without human intervention," Nat. Photon., Vol. 14, 383–390, 2020.

- Zhen, Z., C. Qian, Y. Jia, Z. Fan, R. Hao, T. Cai, B. Zheng, H. Chen, and E. Li, "Realizing 8. transmitted metasurface cloak by a tandem neural network," Photon. Res., Vol. 9, B229–B235, 2021.

- 9. Qian, C. and H. Chen, "A perspective on the next generation of invisibility cloaks Intelligent cloaks," Appl. Phys. Lett., Vol. 118, 180501, 2021.

- 10. Wang, Z., C. Qian, T. Cai, L. Tian, Z. Fan, J. Liu, Y. Shen, L. Jing, J. Jin, E. Li, B. Zheng, and H. Chen, "Demonstration of spider-eyes-like intelligent antennas for dynamically perceiving incoming waves," Adv. Intell. Syst., Vol. 3, 2100066, 2021.

- Cai, T., S. Tang, B. Zheng, G. Wang, W. Ji, C. Qian, Z. Wang, E. Li, and H. Chen, "Ultrawideband 11. chromatic aberration-free meta-mirrors," Adv. Photon., Vol. 3, 016001, 2021.

- 12. Huang, M., B. Zheng, T. Cai, X. Li, J. Liu, C. Qian, and H. Chen, "Machine-learning-enabled metasurface for direction of arrival estimation," Nanophotonics, Vol. 11, No. 9, 2022.

- Jia, Y., C. Qian, Z. Fan, Y. Ding, Z. Wang, D. Wang, E. Li, B. Zheng, T. Cai, and H. Chen, "In-situ customized illusion enabled by global metasurface reconstruction," *Adv. Funct. Mater.*, Vol. 2109331, 1–7, 2022.

- Ma, W., F. Cheng, and Y. Liu, "Deep-learning-enabled on-demand design of chiral metamaterials," ACS Nano, Vol. 12, 6326–6334, 2018.

- 15. Malkiel, I., M. Mrejen, A. Nagler, U. Arieli, L. Wolf, and H. Suchowski, "Plasmonic nanostructure design and characterization via Deep Learning," *Light: Sci. Appl.*, Vol. 7, 60, 2018.

- 16. Ma, W., F. Cheng, Y. Xu, Q. Wen, and Y. Liu, "Probabilistic representation and inverse design of metamaterials based on a deep generative model with semi-supervised learning strategy," *Adv. Mater.*, Vol. 31, 1901111, 2019.

- 17. Liu, Z., D. Zhu, K. T. Lee, A. S. Kim, L. Raju, and W. Cai, "Compounding meta-atoms into metamolecules with hybrid artificial intelligence techniques," *Adv. Mater.*, Vol. 32, 1904790, 2020.

- Ma, W., Z. Liu, Z. A. Kudyshev, A. Boltasseva, W. Cai, and Y. Liu, "Deep learning for the design of photonic structures," *Nat. Photon.*, Vol. 15, 77–90, 2021.

- Ma, W., Y. Xu, B. Xiong, L. Deng, R. Peng, M. Wang, and Y. Liu, "Pushing the limits of functionality-multiplexing capability in metasurface design based on statistical machine learning," *Adv. Mater.*, Vol. 34, 2110022, 2022.

- 20. Qiu, T., X. Shi, J. Wang, Y. Li, S. Qu, Q. Cheng, T. Cui, and S. Sui, "Deep learning: A rapid and efficient route to automatic metasurface design," *Adv. Sci.*, Vol. 6, 1900128, 2019.

- Zhu, R., T. Qiu, J. Wang, S. Sui, C. Hao, T. Liu, Y. Li, M. Feng, A. Zhang, C. Qiu, and S. Qu, "Phase-to-pattern inverse design paradigm for fast realization of functional metasurfaces via transfer learning," *Nat. Commun.*, Vol. 12, 2974, 2021.

- Tan, Q., B. Zheng, T. Cai, C. Qian, R. Zhu, X. Li, and H. Chen, "Broadband spin-locked metasurface retroreflector," Adv. Sci., Vol. 2201397, 1–7, 2022.

- Hua, Y., C. Qian, H. Chen, and H. Wang, "Experimental topology-optimized cloak for water waves," *Mater. Today Phys.*, Vol. 27, 100754, 2022.

- 24. Fan, Z., C. Qian, Y. Jia, Z. Wang, Y. Ding, D. Wang, L. Tian, E. Li, T. Cai, B. Zheng, I. Kaminer, and H. Chen, "Homeostatic neuro-metasurfaces for dynamic wireless channel management," *Sci. Adv.*, Vol. 8, eabn7905, 2022.

- 25. Qian, C., Z. Wang, H. Qian, T. Cai, B. Zheng, X. Lin, Y. Shen, I. Kaminer, E. Li, and H. Chen, "Dynamic recognition and mirage using neuro-metamaterials," *Nat. Commun.*, Vol. 13, 2694, 2022.

- Qian, C., Y. Yang, Y. Hua, C. Wang, X. Lin, T. Cai, D. Ye, E. Li, I. Kaminer, and H. Chen, "Breaking the fundamental scattering limit with gain metasurfaces," *Nat. Commun.*, Vol. 13, 4383, 2022.

- Yang, Y., L. Jing, B. Zheng, R. Hao, W. Yin, E. Li, C. M. Soukoulis, and H. Chen, "Full-polarization 3D metasurface cloak with preserved amplitude and phase," *Adv. Mater.*, Vol. 28, 6866–6871, 2016.

- 28. Chen, H., L. Ran, J. Huangfu, X. Zhang, K. Chen, T. M. Grzegorczyk, and J. A. Kong, "Lefthanded materials composed of only S-shaped resonators," *Phys. Rev. E*, Vol. 70, 057605, 2004.

- Chen, H., B. Zheng, L. Shen, H. Wang, X Zhang, N. I. Zheludev, and B. Zhang, "Ray-optics cloaking devices for large objects in incoherent natural light," *Nat. Commun.*, Vol. 4, 1–6, 2013.

- Camacho, M., B. Edwards, and N. Engheta, "A single inverse-designed photonic structure that performs parallel computing," *Nat. Commun.*, Vol. 12, 1466, 2021.

- Zhu, T., Y. Zhou, Y. Lou, H. Ye, M. Qiu, Z. Ruan, and S. Fan, "Plasmonic computing of spatial differentiation," *Nat. Commun.*, Vol. 8, 15391, 2017.

- Khoram, E., A. Chen, D. Liu, L. Ying, Q. Wang, M. Yuan, and Z. Yu, "Nanophotonic media for artificial neural inference," *Photon. Res.*, Vol. 7, 823–827, 2019.

- Zhu, Z., W. Ye, J. Ji, X. Yuan, and C. Zen, "High-contrast light-by-light switching and AND gate based on nonlinear photonic crystals," *Opt. Express*, Vol. 14, 1783–1788, 2006.

- 34. McCutcheon, M. W., G. W. Rieger, J. F. Young, D. Dalacu, P. J. Poole, and R. L. Williams, "Alloptical conditional logic with a nonlinear photonic crystal nanocavity," *Appl. Phys. Lett.*, Vol. 95, 221102, 2009.

- 35. Liu, Q., Z. Ouyang, C. Wu, C. Liu, and J. C. Wang, "All optical half adder based on cross structures in two-dimensional photonic crystals," *Opt. Express*, Vol. 16, 18992–19000, 2008.

- Ishizaka, Y., Y. Kawaguchi, K. Saitoh, and M. Koshiba, "Design of ultra compact all-optical XOR and AND logic gates with low power consumption," Opt. Commun., Vol. 284, 3528–3533, 2011.

- 37. Wei, H., Z. Li, X. Tian, Z. Wang, F. Cong, N. Liu, S. Zhang, P. Nordlander, N. J. Halas, and H. Xu, "Quantum dot based local field imaging reveals plasmon-based interferometric logic in silver nanowire networks," *Nano Lett.*, Vol. 11, 471–475, 2011.

- 38. Fu, Y., X. Hu, and Q. Gong, "Silicon photonic crystal all optical logic gates," *Phys. Lett. A*, Vol. 377, 329–333, 2013.

- 39. Wang, H., X. Yu, and X. Rong, "All-optical AND, XOR, and NOT logic gates based on Y-branch photonic crystal waveguide," *Opt. Eng.*, Vol. 54, 077101, 2015.

- 40. Fan, R., X. Yang, X. Meng, and X. Sun, "2D photonic crystal logic gates based on self-collimated effect," J. Phys. D: Appl. Phys., Vol. 49, 325104, 2016.

- 41. Sang, Y., X. Wu, S. S. Raja, C. Wang, H. Li, Y. Ding, D. Liu, J. Zhou, H. Ahn, S. Gwo, and J. Shi "Broadband multifunctional plasmonic logic gates," *Adv. Opt. Mater.*, Vol. 6, 1701368, 2018.

- 42. Manjappa, M., P. Pitchappa, N. Singh, N. Wang, N. I. Zheludev, C. Lee, and R. Singh, "Reconfigurable MEMS Fano metasurfaces with multiple-input-output states for logic operations at terahertz frequencies," *Nat. Commun.*, Vol. 9, 4056, 2018.

- Qian, C., X. Lin, X. Lin, J. Xu, Y. Sun, E. Li, B. Zhang, and H. Chen, "Performing optical logic operations by a diffractive neural network," *Light: Sci. Appl.*, Vol. 9, 59, 2020.

- 44. He, Y., P. Wang, C. Wang, J. Liu, H. Ye, X. Zhou, Y. Li, S. Chen, X. Zhang, and D. Fan, "All-optical signal processing in structured light multiplexing with dielectric meta-optics," *ACS Photon.*, Vol. 7, 135, 2020.

- Dang, Z., T. Chen, Z. Ding, Z. Liu, X. Zhang, X. Jiang, and Z. Zhang, "Multiport all-logic optical switch based on thermally altered light paths in a multimode waveguide," *Opt. Lett.*, Vol. 46, 3025–3028, 2021.

- 46. Chao, M., B. Cheng, Q. Liu, W. Zhang, Y. Xu, and G. Song, "Novel optical XOR/OR logic gates based on topologically protected valley photonic crystals edges," *J. Opt.*, Vol. 23, 115002, 2021.

- Zhao, Z., Y. Wang, X. Ding, H. Li, J. Fu, K. Zhang, S. N. Burokur, and Q. Wu, "Compact logic operator utilizing a single-layer metasurface," *Photon. Res.*, Vol. 10, 316–322, 2022.

- 48. Jensen, J. S. and O. Sigmund, "Topology optimization for nano-photonics," *Laser Photon. Rev.*, Vol. 5, 308–321, 2011.

- 49. Rodríguez, J. A., A. I. Abdalla, B. Wang, B. Lou, S. Fan, and M. A. Cappelli, "Inverse design of plasma metamaterial devices for optical computing," *Phys. Rev. Applied*, Vol. 16, 014023, 2021.

- 50. Chung, H., J. Park, and S. V. Boriskina, "Inverse-designed waveguide-based biosensor for high-sensitivity, single-frequency detection of biomolecules," *Nanophotonics*, Vol. 11, 1427–1442, 2022.