# Design of Quasi-Equal Inductor Filter Based on Multilayer Substrate

# Ke Cao\* and Kun Pan

Abstract—A quasi-equal inductor filter and its corresponding multilayer realization are proposed in this paper. The circuit transformation is performed using the Norton transformation. In the proposed filter, ratio between the largest and smallest component values is reduced, which makes the design of components much easier. Meanwhile, by carefully selecting the transformation ratio, all grounding inductors are equal in value. As a result, the multilayer filter design is simplified because only one instance of grounding inductors needs to be designed instead of three. An experimental prototype is fabricated and measured. The measurement result agrees well with the desired one, which shows the effectiveness of proposed filter.

#### 1. INTRODUCTION

In a wireless communication system, filters play a crucial role in eliminating unwanted signals and improving signal quality. Multilayered filters are widely used due to their high performance, low cost, and compact size. However, the design of multilayer filters can be challenging because of the presence of multiple components that need to be designed individually and the existence of parasitic effects [1]. Even simple structures like metal strips or vias can introduce parasitic effects [2,3], let alone components with more complex structures [4]. To simplify the design process of multilayer filters, various methods have been proposed. In [1] and [5], equivalent circuits are used for evaluating the performance of the networks. In [6], the theoretical foundation without considering parasitic effects is discussed first. Then the real component models with parasitic effects are discussed.

In this paper, a quasi-equal inductor filter is proposed, and corresponding multilayer filter is designed. The Norton transformation is used in circuit transformation. In this way, the ratio between the largest and smallest components are obviously reduced. Meanwhile, the grounding inductors are equal in value. As a result, the design process of multilayer filter is obviously simplified. An experimental prototype is fabricated and measured. The measured results agree well with the circuit results, which shows the effectiveness of proposed filter.

#### 2. PROPOSED FILTER AND ADVANTAGES

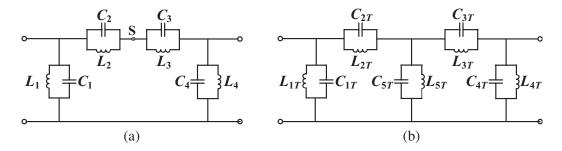

Figure 1(a) shows the initial third-order elliptic filter circuit. With the equations given in [7], a filter operating at 800 MHz with 120 MHz 3 dB-bandwidth and 50 dB out-of-band suppression is designed. The component values for the filter are  $L_1 = 1.15 \,\text{nH}$ ,  $L_2 = 31.0 \,\text{nH}$ ,  $L_3 = 16.2 \,\text{nH}$ ,  $L_4 = 1.15 \,\text{nH}$ ,  $C_1 = 34.4 \,\text{pF}$ ,  $C_2 = 2.44 \,\text{pF}$ ,  $C_3 = 1.28 \,\text{pF}$ , and  $C_4 = 34.4 \,\text{pF}$ .

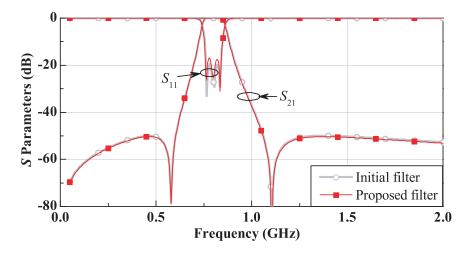

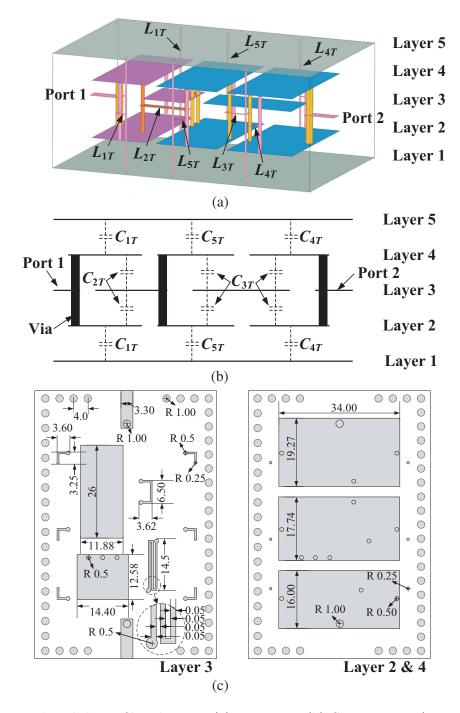

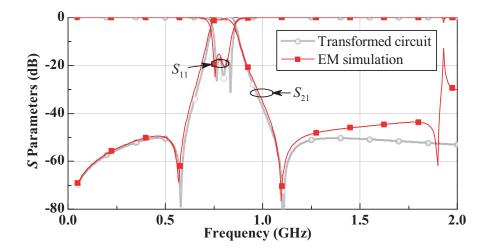

Figure 1(b) shows the proposed quasi-equal inductor filter, which was obtained by applying the Norton transformation to the initial filter. Its component values are  $L_{1T} = L_{4T} = L_{5T} = 1.27 \,\mathrm{nH}$ ,  $L_{2T} = 8.96 \,\mathrm{nH}$ ,  $L_{3T} = 4.49 \,\mathrm{nH}$ ,  $C_{1T} = 28.4 \,\mathrm{pF}$ ,  $C_{2T} = 8.44 \,\mathrm{pF}$ ,  $C_{3T} = 4.62 \,\mathrm{pF}$ ,  $C_{4T} = 34.2 \,\mathrm{pF}$ ,  $C_{5T} = 31.5 \,\mathrm{pF}$ . Fig. 2 compares the responses before and after transformation. Good agreement between them can be easily observed.

Received 15 February 2023, Accepted 27 March 2023, Scheduled 13 April 2023

<sup>\*</sup> Corresponding author: Ke Cao (caoke@jit.edu.cn).

The authors are with the School of Electronic and Information Engineering, Jinling Institute of Technology, Nanjing, China.

Figure 1. Filter circuit. (a) Initial filter. (b) Proposed filter.

Figure 2. Frequency responses before and after transformation.

The proposed filter has three advantages compared to the initial filter.

- 1. The ratio between the largest and smallest capacitors and inductors has been reduced, making it easier to design the corresponding multilayer components. For example, in the initial filter,  $C_{\rm max}/C_{\rm min} = C_4/C_3 = 26.8$  and  $L_{\rm max}/L_{\rm min} = L_2/L_1 = 27.0$ . In the proposed filter,  $C_{\rm max}/C_{\rm min} = C_{4T}/C_{3T} = 7.40$  and  $L_{\rm max}/L_{\rm min} = L_{2T}/L_{1T} = 7.06$ .

- 2. The grounding inductors  $(L_{1T}, L_{4T}, \text{ and } L_{5T})$  have equal values. In multilayer filter design, these inductors may have the same structure and dimensions, which simplifies the design process.

- 3. The stray capacitance between the S point (Fig. 1(a)) and ground is eliminated.

# 3. CIRCUIT TRANSFORMATION THEORY

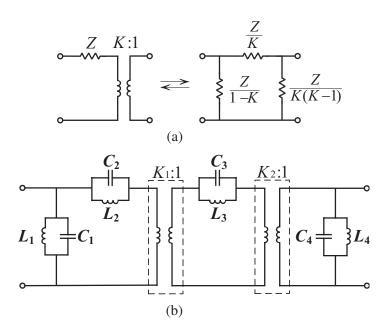

The proposed circuit was obtained using the Norton transformation [7]. As shown in Fig. 3(a), with the Norton transformation, the series impedance can be transformed into a  $\pi$ -network. The transformation ratio is represented by K. Depending on the value of K, the equivalent  $\pi$ -network contains one negative element that is not realizable. However, in the filter circuit, it can be lumped by adjacent positive component.

For example, in the initial filter, two hypothetical transformers are introduced, as shown in Fig. 3(b). Their transformation ratios are noted as  $K_1$  and  $K_2$ , respectively. Applying the Norton transformation and simplifying the circuit, we can get the proposed filter circuit.

By setting  $K_1 K_2 = 1 \tag{1}$

we can ensure that the frequency response remains unchanged before and after the transformation. The

**Figure 3.** Circuit transformation. (a) Norton transformation. (b) Initial circuit with two hypothetical transformers.

transformed component values can be determined by:

$$L_{1T} = \frac{L_1 L_2}{(1 - K_1)L_1 + L_2} \tag{2}$$

$$L_{2T} = \frac{L_2}{K_1} \tag{3}$$

$$L_{3T} = \frac{L_3}{K_1^2 K_2} \tag{4}$$

$$L_{4T} = \frac{L_3 L_4}{K_1^2 K_2 [K_2 (L_3 + L_4) - L_4]}$$

(5)

$$L_{5T} = \frac{L_2 L_3}{K_1 [K_1 (L_2 + L_2) - K_1 K_2 L_2 - L_2]}$$

(6)

$$C_{1T} = C_1 + (1 - K_1)C_2 \tag{7}$$

$$C_{2T} = K_1 C_2 \tag{8}$$

$$C_{3T} = K_1^2 K_2 C_3 (9)$$

$$C_{4T} = K_1^2 K_2 [K_2 (C_3 + C_4) - C_3] (10)$$

$$C_{5T} = K_1[K_1(C_2 + C_3) - K_1K_2C_3 - C_2]$$

(11)

The next step is to make the grounding inductors  $L_{1T}$ ,  $L_{4T}$ , and  $L_{5T}$  equal in value. To achieve this, we may solve the following equations for  $K_1$  and  $K_2$ :

$$\begin{cases}

L_{1T} = L_{4T} \\

L_{1T} = L_{5T}

\end{cases}$$

(12)

Using the numerical solver software, we have  $K_1 = 3.4596$ ,  $K_2 = 0.3014$  in this example. With these values, all the transformed component values can be calculated using Equations (2)–(11).

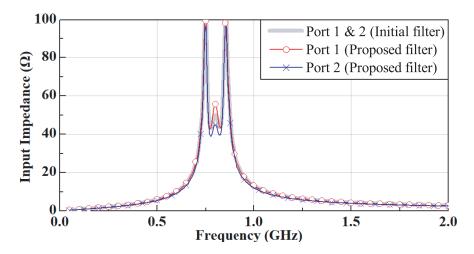

It should be noted that the method used results in  $K_1K_2 = 1.043 \neq 1$ . As a result, the input impedance of the transformed filter is not equal to  $50 \Omega$ . As shown in Fig. 4, the input impedances at the operating frequencies of Port 1 and Port 2 are about  $55 \Omega$  and  $45 \Omega$ , respectively. However, in the design of multilayer filters, fine-tunings are essential. The slight deviation in input impedance can be

Figure 4. Input impedance before and after transformation.

compensated during this process. Therefore, it is acceptable to slightly sacrifice the accuracy of the input impedance for equal inductor values.

#### 4. MULTILAYER FILTER DESIGN

Based on the proposed filter circuit, a multilayer filter layout is designed, as shown in Fig. 5(a). The substrate used is 1 mm-thickness Rogers RT/duroid 5880 Laminate, whose dielectric constant is 2.2, and loss tangent is 0.004.

The multilayer filter is composed of five metal layers interleaved with four dielectric layers. The first and fifth metal layers are grounds. Fig. 5(b) shows a section view that highlights the structure of capacitors.

The grounding capacitors  $C_{1T}$ ,  $C_{4T}$ , and  $C_{5T}$  have relatively large values. They are designed as two parallel sub-capacitors. Each pair of sub-capacitors is placed at the top and bottom of the layout, connected by a via. To reduce the parasitic inductance, the diameter of the vias is increased deliberately.  $C_{2T}$  is designed as a 3-layer vertical-integrated-capacitor (VIC). It is located on layers 2 to layer 4 of the layout. It shares the electrodes on the second and fourth layers with  $C_{1T}$ , which makes the structure more compact.  $C_{3T}$  is the smallest capacitor. Its value is only about half of that of  $C_{2T}$ . If it were simply designed as a 3-layer VIC, its dimensions would be very small, and its capacitance would be easily influenced by parasitic effects and fabricating errors. To increase its dimensions appropriately,  $C_{3T}$  was designed as 3-layer VICs connected in series. Each of them has a similar structure to  $C_{2T}$ , but its capacitance is twice that of  $C_{3T}$ . In this way, the capacitance of  $C_{3T}$  remains unchanged, and its dimensions are increased.

All the inductors are composed of meandered lines and vias [8]. The meandered lines are placed on the third layer of the layout to decrease the coupling between the meandered lines and grounds. Because the inductor values of  $L_{1T}$ ,  $L_{4T}$ , and  $L_{5T}$  are the same, they have the same structure and dimensions during the whole design process. Because only one grounding inductor needs to be designed instead of three, the design process is further simplified.

The input and output ports are designed as striplines with a characteristic impedance of  $50 \Omega$ . The strip is located on the third layer of the layout, while the first and fifth layers serve as the grounds [9]. Port 1 is connected to the via of  $C_{1T}$ , and Port 2 is connected to the via of  $C_{4T}$ . To achieve field confinement, a via fence, which connects two ground planes, is adopted to surround the whole model except for two ports.

Based on the proposed layout, a multilayer filter was designed and optimized. The initial dimensions of the multilayer capacitors were calculated using the equation  $C = \epsilon S/d$ . The initial dimensions of multilayer inductors were designed individually using the method given in [10]. Then all of these components were integrated into the layout. electromagnetic (EM) simulation software was used for

**Figure 5.** Proposed multilayer filter layout. (a) 3D view. (b) Section view (capacitors only). (c) Component dimensions (Unit: mm).

simulation and optimization. Because the structure and dimensions of  $L_{1T}$ ,  $L_{4T}$ , and  $L_{5T}$  are the same, designing and optimizing only one instance of them suffices, which makes the design and optimization process easier. Fig. 5(c) shows the dimensions of multilayer components.

Figure 6 shows the final EM simulation results and circuit results. Good agreement between them can be observed. Due to the introduction of via fence, a resonance cavity is formed by the two ground planes and the via fence. The resonance at 1.9 GHz is caused by this resonance cavity. Adjusting the position of the via fence can adjust this undesired resonance.

Figure 6. Circuit results and EM simulation results of proposed multilayer filter.

#### 5. EXPERIMENTAL RESULT

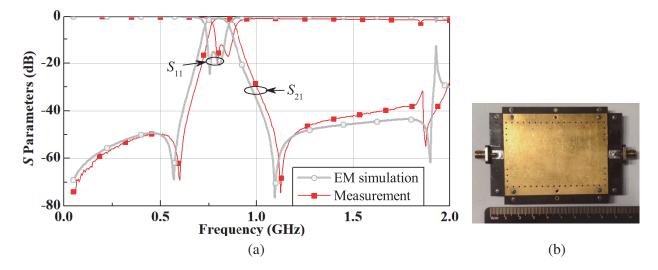

An experimental prototype is fabricated using printed circuit board (PCB) technology, and every layer is manually stacked. The core size of the prototype is about  $4.8\,\mathrm{cm}\times6.4\,\mathrm{cm}\times0.4\,\mathrm{cm}$  or  $7.62\times10^{-4}\lambda_g$ . As shown in Fig. 7, the measurement results are in good agreement with the simulation ones, except for a minor frequency shift and the resonance at about 1.9 GHz. The frequency shift may be caused by the errors in manual stacking of the PCBs. The measured central frequency and 3 dB bandwidth are 822 MHz and 123 MHz, respectively. The designed central frequency and 3 dB bandwidth are 795 MHz and 118 MHz, respectively. The quality factor of both the designed filter and the experimental prototype is approximately 6.68. The insertion loss of the designed filter and the experimental prototype are about 0.80 dB and 0.83 dB, respectively. The return loss of the designed filter and the experimental prototype are about 15.5 dB and 12.6 dB, respectively. The good agreement between desired response and measured response shows the effectiveness of the proposed filter. Table 1 compares the proposed filter with some state-of-the-art filters.

Figure 7. Experimental prototype. (a) Measurement results. (b) Photograph.

| Ref.                                            | $f_0$ (GHz) | FBW (%) | IL (dB) | RL (dB) | Size $(\times 10^{-3} \lambda_g)$ | Fabrication Process |

|-------------------------------------------------|-------------|---------|---------|---------|-----------------------------------|---------------------|

| [1]                                             | 10          | Tunable | 4.1     | 20*     | 8.8                               | GaAs pHEMT          |

| [3]                                             | 6.5         | 4       | 2.4     | 18      | 1.31                              | LTCC                |

| [8]                                             | 4.03        | 50.2    | -       | -       | 0.705                             | LTCC                |

| [10]                                            | 1.64        | 9.1*    | 2.8     | 21.3    | 0.006                             | LTCC                |

| [11]                                            | 2.001       | 133.7   | 0.65    | 13.68   | 8.1                               | PCB                 |

| [12]                                            | 31          | 11.7    | 2.7     | 24      | -                                 | LTCC                |

| Simulation                                      | 0.796       | 14.8    | 0.80    | 15.5    | 0.762                             | PCB                 |

| Measurement                                     | 0.822       | 14.9    | 0.83    | 12.6    | 0.762                             | PCB                 |

| Data with * were estimated from the literature. |             |         |         |         |                                   |                     |

**Table 1.** Comparison with related researches.

#### 6. CONCLUSION

In this paper, a quasi-equal inductor filter is proposed, which utilizes the Norton transformation. By the careful selection of transformer ratios, the ratio between the largest and smallest components is obviously reduced, and all grounding inductors are made equal in value. As a result, the design of a multilayer filter can be simplified. A multilayer filter is designed on the proposed circuit. An experimental prototype was fabricated using PCB technology, and the measurement results show good agreement with the desired response, except for a small frequency shift. This demonstrates the effectiveness of the proposed filter design.

## ACKNOWLEDGMENT

This work was supported by the Scientific Research Foundation for Doctors of Jinling Institute of Technology, Grant Number: JIT-B-201821.

# REFERENCES

- 1. Zhu, H., X. Ning, Z. Huang, and X. Wu, "An ultra-compact on-chip reconfigurable bandpass filter with semi-lumped topology by using GaAs pHEMT technology," *IEEE Access*, Vol. 8, 31606–31613, 2020.

- 2. Neculoiu, D., A. Bunea, A. M. Dinescu, and L. A. Farhat, "Band pass filters based on GaN/Si lumped-element SAW resonators operating at frequencies above 5 GHz," *IEEE Access*, Vol. 6, 47587–47599, 2018.

- 3. Zhu, L., "Narrowband LTCC filter with length-reduced end-coupled resonators," *Progress In Electromagnetics Research Letters*, Vol. 93, 13–19, 2020.

- 4. Xie, N., H. Tie, Q. Ma, and B. Zhou, "Spur-less interdigital metal-insulator-metal capacitor," *Progress In Electromagnetics Research Letters*, Vol. 101, 49–54, 2021.

- 5. Kewei, Q., "Miniaturised LTCC diplexer with low insertion loss for LTE application," *Electronics Letters*, Vol. 56, No. 1, 39–41, 2020.

- 6. Borah, D. and T. S. Kalkur, "Temperature effect on a lumped element balanced dual-band band-stop filter, *Progress In Electromagnetics Research M*, Vol. 97, 107–117, 2020.

- 7. Zverev, A. I. Handbook of Filter Synthesis, Wiley, New York, 1967.

- 8. Wu, D., Y. C. Li, Q. Xue, and J. Mou, "LTCC bandstop filters with controllable bandwidths using transmission zeros pair," *IEEE Transactions on Circuits and Systems II: Express Briefs*, Vol. 67, No. 6, 1034–1038, 2019.

9. A. Gámez-Machado, D. Valdés-Martín, A. Asensio-López, and J. Gismero-Menoyo, "Microstripto-stripline planar transitions on LTCC," 2011 IEEE MTT-S International Microwave Workshop Series on Millimeter Wave Integration Technologies, 1–4, Sitges, Spain, 2011.

- 10. Brzezina, G., L. Roy, and L. MacEachern, "Design enhancement of miniature lumped-element LTCC bandpass filters," *IEEE Transactions on Microwave Theory and Techniques*, Vol. 57, No. 4, 815–823, 2009.

- 11. Yang, L., L. Zhu, R. Zhang, J. Wang, W. Choi, K. Tam, and R. Gómez-García, "Novel multilayered ultra-broadband bandpass filters on high-impedance slotline resonators," *IEEE Transactions on Microwave Theory and Techniques*, Vol. 67, No. 1, 129–139, 2019.

- 12. Sun, F., H. Zhu, X. Zhu, Y. Yang, and R. Gómez-García, "Design of on-chip millimeter-wave bandpass filters using multilayer patterned-ground element in 0.13-μm (Bi)-CMOS technology," *IEEE Transactions on Microwave Theory and Techniques*, Vol. 67, No. 12, 5159–5170, 2019.