(Received 3 March 2025, Accepted 11 April 2025, Scheduled 24 April 2025)

# Minimum-Current-Stress Strategy for Modular Multilevel Type DC-DC Converter Based on Long Short-Term Memory Optimization

Dazhuan Yu, Xin Chow\*, Zefeng Lin, and Xiaobing Niu

College of Marine Electrical Engineering, Dalian Maritime University, China

ABSTRACT: Current stress has a significant impact on the operation of power electronic devices, and the reduction of current stress can improve the safety and reliability of the system. First, this paper proposes a novel asymmetric duty cycle modulation strategy for the primary side of a modular multilevel converter type (MMC) dual active bridge converter (DAB) to increase the control freedom of the primary side. Secondly, a novel optimization strategy based on a long short-term memory network (LSTM) classification is proposed in this paper to optimize the current stress. The output power of the system is classified by LSTM, and minimum current stresses at different powers are optimized by a novel meta-heuristic iterative optimization based on generalized quadratic interpolation (GQI). Finally, the feasibility of the scheme is verified by hardware-in-the-loop experiments.

#### 1. INTRODUCTION

ual active bridge (DAB) is widely used due to its advantages such as current isolation and high efficiency [1, 2]. The optimization objective is converter inductor current stress. The output voltage of a conventional DAB is usually controlled by single phase shift (SPS) control [3-5]. Refs. [15, 16] proposed that after modeling the SPS control of the converter, the system generates excessive current stresses when the voltages are not matched. In [6, 7], the flexibility of the system can be improved by adding one more degree of freedom, i.e., extended phase shift (EPS) control, which significantly reduces the current stress compared to SPS. Triple phase shift (TPS) control is proposed in [8–10], where two different control degrees of freedom are added to the primary and secondary sides, respectively, which further optimizes the current stress of the system. TPS and combining Lagrange multiplier with proportional-integral (PI) controller for current stress optimization was proposed in [17, 19].

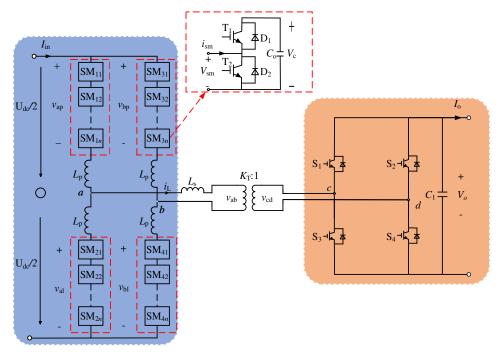

The above shows the optimization of inductor current stress in conventional topology. Refs. [11–13] introduced multilevel topologies in DABs to reduce the voltage stress on the switching devices. Modular multilevel converters (MMCs) have been introduced in DAB topologies due to high modularity and high level of availability [14]. As shown in Figure 1, each phase consists of two bridge arms, with each connected in series with N half-bridge submodules (SMs), while increasing the control degrees of freedom. In [31], a novel partial power DAB converter is proposed that combines the best characteristics of MMC-DAB and autotransformer thereof to minimize the current stress at all operating points. In [32], a multilevel DAB

converter with stepped wave modulation is proposed, where the system switching tubes operate in soft-switching mode, and can greatly optimize the system current stress. In [33], a modulation strategy with variable duty cycle is proposed, which can effectively optimize the inductor current stress and counteract the degradation of the soft-switching characteristics. The introduction of artificial intelligence methods has brought many options for optimal control. Refs. [18, 20] proposed a particle swarm optimization (PSO)-based current stress minimization scheme, which reduced system losses and improved power conversion efficiency. Ref. [34] proposed a differential evolutionary algorithm based on data fine-tuning to optimize current stress. In [35], the objective function is minimized by PSO, and the data-driven model is developed by using the optimal dataset, which greatly reduces the converter current stress. As mentioned above, the current stress optimization method for multilevel DAB has become increasingly mature, but the current stress optimization method for MMC-DAB has not yet been studied in depth, and most of the AI optimization algorithms in this area focus on PSO algorithm. In this paper, a current stress optimization method based on generalized quadratic interpolation (GQI) is proposed, which has lower complexity and fewer iterations than PSO and is more suitable for MMC-DAB converters.

Section 1 offers an introduction. Section 2 focuses on the symmetric strategies and novel asymmetric duty cycle modulation strategies for MMC-DAB. Section 3 discusses the classification prediction based on LSTM. Section 4 introduces the inductor current stress optimization strategy about GQI optimization. Section 5 shows the results of hardware-in-the-loop experiments.

<sup>\*</sup> Corresponding author: Xin Chow (Xinchow@dlmu.edu.cn).

FIGURE 1. MMC-DAB topology.

# 2. MODULATION STRATEGY FOR MMC-DAB

# 2.1. Duty Cycle Symmetric Modulation Strategy for MMC-DAB

The constraints can be obtained as follows:

$$\begin{cases} 0 \le D_0, D_1, D_2 \le 0.5 \\ 0 \le d_0, d_1 \le 0.5 \end{cases} \tag{1}$$

where  $D_0$ ,  $D_1$ , and  $D_2$  are the duty cycles of 0, 1/2, and 1 levels of the primary output, respectively, and  $d_0$  and  $d_1$  are the duty cycles of 0 and 1 levels of the secondary output, respectively.

The expression of inductor current and transmitted power can be obtained as follows:

$$\begin{cases} v_{ab} = B_n \sin n\omega t \\ v_{cd} = b_n \sin n\omega (t - d_f T_{hs}) \end{cases}$$

(2)

The inductor current and transmitted power expressions can be deduced as follows:

$$\begin{cases} i\left(t\right) = \sum_{n=1,3,5\cdots}^{\infty} \frac{\sqrt{A^2 + B^2} \sin[n\omega t + (\arctan B/A)]}{n\omega L_S} \\ P = \sum_{n=1,3,5\cdots}^{\infty} \frac{K_T b_n B_n}{2n\omega L_S} \sin(nd_f \pi) \end{cases}$$

(3)

$\omega$ ,  $L_S$ ,  $d_f$ ,  $K_T$ , and  $T_{hs}$  represent the angular frequency, transmission inductance, shift ratio between the primary and secondary edges, transformer ratio, and half a switching cycle, respectively.

$$\begin{cases}

A = 4b_n \sin n\pi d_f \\

B = 4b_n \cos n\pi d_f - B_n \\

B_n = \frac{2U_{dc}}{n\pi} \left[\cos n\pi D_0 + \cos n\pi (D_0 + D_1)\right] \\

b_n = \frac{4V_0}{n\pi} \cos n\pi d_0

\end{cases}$$

(4)

#### 2.2. Asymmetric Duty Cycle Modulation Strategy for MMC-DAB

The 0, 1/2, and 1 levels will each appear twice in half of a cycle, which is different from the modulation of symmetrical duty.

$$\begin{cases}

D_0 + D_1 + D_2 = 0.5 \\

D_{0r} + D_{1r} + D_{2r} = 0.5 \\

D_0 \neq D_{0r}, D_1 \neq D_{1r}, D_2 \neq D_{2r}

\end{cases}$$

(5)

Among them,  $D_0$ ,  $D_1$ , and  $D_2$  are the duty ratios of the first 0, 1/2, and 1 levels in the half cycle of the MMC side, respectively.  $D_{0r}$ ,  $D_{1r}$ , and  $D_{2r}$  are the duty ratios of the last 0, 1/2, and 1 levels in the half cycle, respectively. High-frequency transformer primary and secondary voltages, inductor current, and transmitted power are the same as those in Eqs. (4) and (5), but the coefficients B and  $B_n$  are not the same as those in Eqs. (4) and (5) because they need to be according to the asymmetric modulation strategy. At this time there are:

$$\begin{cases} B = 4b_n \cos n\pi d_f - B_n \\ B_n = \frac{V_{dc}}{n\pi} [\cos n\pi D_0 + \cos n\pi (D_0 + D_1) \\ + \cos n\pi D_{0r} + \cos n\pi (D_{0r} + D_{1r})] \end{cases}$$

(6)

## 3. LSTM-BASED CLASSIFICATION PREDICTION

#### 3.1. Working Principle of LSTM

LSTM is a variant of recurrent neural network (RNN) [21], which reduces overfitting by introducing gating mechanisms, and [24] lists the structure of LSTM and the expressions of each gating mechanism.

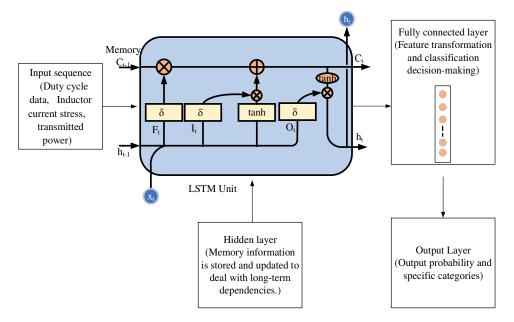

FIGURE 2. LSTM classification prediction steps.

**TABLE 1**. LSTM classification prediction pesudocode.

```

Pseudo-code of LSTM Classification forecasts

Setting up the dataset

model = Sequential()

model.add(LSTM(units = lstm_units, input_shape = (seq_length, input_dim)))

Add Dropout layer (to prevent overfitting)

model.add(Dropout(rate = 0.2))

model.add(Dense(units = num_classes, activation = 'softmax'))

history = model.fit(X_train, y_train, epochs = epochs, batch_size = batch_size, validation_split = 0.2)

loss, accuracy = model.evaluate(X_test, y_test)

print(f'Test Accuracy: {accuracy}'')

predictions = model.predict(X_test)

```

21

#### 3.2. Power Classification Prediction of Current Stress

The training steps of LSTM are shown in Figure 2. The input sequence is preprocessed, such as data normalization and data tile. In the next step of building the LSTM model, the shape of the input layer depends on the feature dimension and sequence length of the input sequence data. The LSTM layer is the core part of the model, which is responsible for extracting the time dependence in the sequence [22]. The hidden layer controls the flow of information, stores and updates information through a series of 'gates' [23]. The long-term dependencies in the sequence are captured by the cell state. The structure of the unit state enables the information to be transmitted more stably. The LSTM classification prediction pseudo-code is shown in Table 1.

$\delta$  is the activation function:  $\delta = 1/(1 + e^{-x})$ .

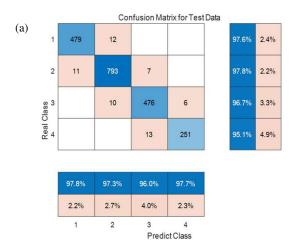

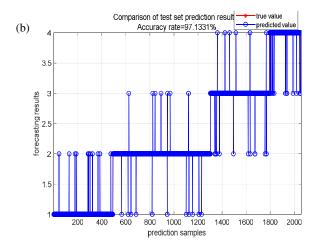

Figure 3 shows the effect of data classification prediction, and categories 1–4 are four power segments from low to high. The accuracy is as high as 97.1331 %. LSTM has a high accu-

racy rate for the classification of current stress duty cycle matrix about load power.

# 4. CURRENT STRESS OPTIMIZATION BASED ON QUADRATIC INTERPOLATION OPTIMIZATION

#### 4.1. Traditional Quadratic Interpolation

Quadratic interpolation is a commonly used curve fitting technique that is commonly used to find the minimum point in a given deterministic initial interval for a unary function [25, 29]. Function f(x) is approximated by a quadratic interpolation polynomial denoted as L(x), L(x), f(x), where  $\alpha$  and  $\beta$  are undetermined coefficients [30]. Let f(x) have three points i, j, and k, and the value of f(x) is equal to the value of the interpolation point L(x), which is expressed as:

$$L(x) = \alpha x^2 + \beta x + C = f(x) \tag{7}$$

The  $\alpha$  and  $\beta$  values represented by i, j, k and their corresponding f(i), f(j), and f(k) can be obtained according to the above

FIGURE 3. LSTM classification prediction results. (a) Test set classification results. (b) Test set classification prediction accuracy.

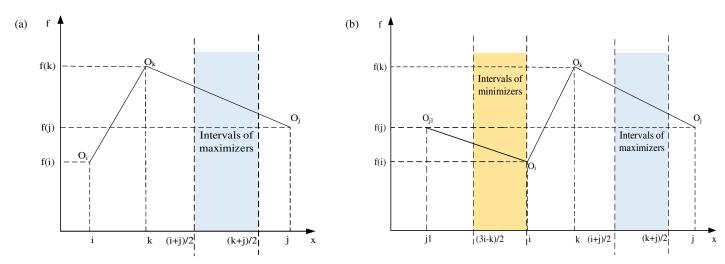

FIGURE 4. Generalized quadratic interpolation strategy. (a) Maximum interval of quadratic interpolation. (b) The minimum intervals of GQI.

formula. Then L(x) can be expressed as:

$$L(x) = \frac{(x-j)(x-k)}{(i-j)(i-k)} f(i) + \frac{(x-i)(x-k)}{(j-i)(j-k)} f(j) + \frac{(x-j)(x-i)}{(k-j)(k-j)} f(k)$$

(8)

# 4.2. A Novel Quadratic Interpolation Optimization

When the minimum value of a one-dimensional dataset is optimized, such as inductor current stress, there will be times when the search area is not selected properly, resulting in only the maximum value in the optimization interval but not the minimum value [27, 28]. For example, for Figure 4(a), where there is only one maximum interval, and the optimal solution of f(x) may be the left of i. When the GQI algorithm [26] is introduced as shown in Figure 4(b), the minimum intervals are supplied by  $O_{j1}$ ,  $O_i$ , and  $O_k$ . The maximum and minimum intervals in Figures 4(a) and 4(b) are calculated as shown in Eqs. (15), (16) and Eq. (21) in [26].

After passing the exploration and development phases, the position of the ith instance was updated as follows. x, v, and t denote the position, iteration speed, and number of iteration rounds, respectively.

$$x_{i}(t+1) = \begin{cases} x_{i}(t) & fit(x_{i}(t)) \le fit(v_{i}(t+1)) \\ v_{i}(t+1) & fit(x_{i}(t)) > fit(v_{i}(t+1)) \end{cases}$$

(9)

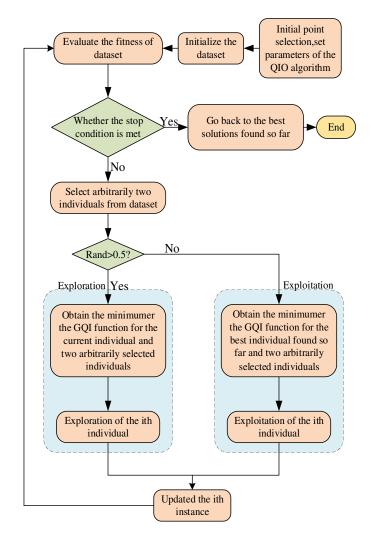

The specific flowchart of quadratic interpolation optimization is as Figure 5.

#### 5. EXPERIMENTAL RESULT AND ANALYSIS

#### 5.1. Hardware-in-the-Loop Experiment Parameters

This hardware-in-the-loop platform uses the Rapid Control Prototype (RCP) to run the overall control section and the Dspace1202 to run the MMC-DAB hardware topology. The sampled physical quantities are communicated to the RCP control section via I/O ports, and the PWM pulse waves generated by the control section are communicated to the Dspace1202 via Modbus TCP/IP. The overall structure of the platform is shown in Figure 6. The experimental parameters are shown in Table 2.

FIGURE 5. QIO specific steps.

FIGURE 6. Hardware-in-the-loop experimental platform.

# 5.2. Optimization of Symmetric Modulation

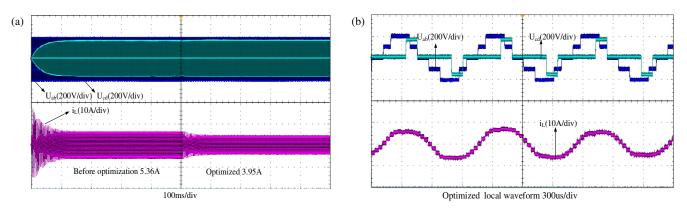

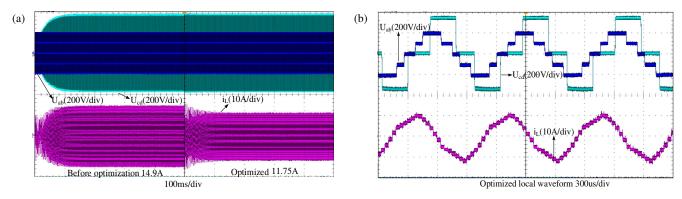

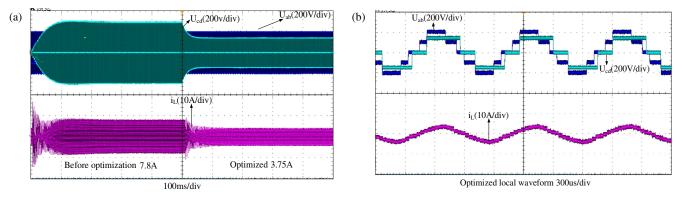

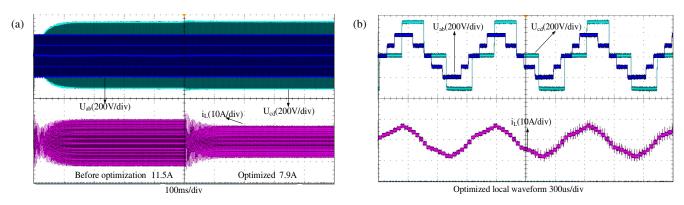

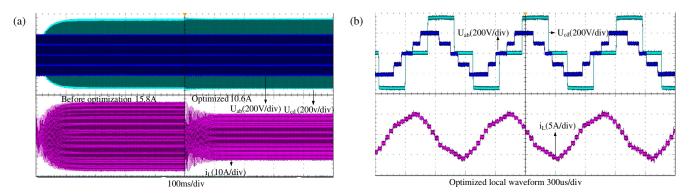

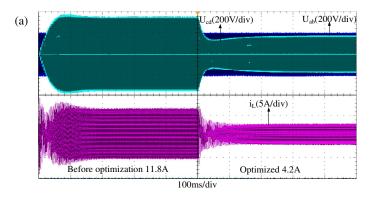

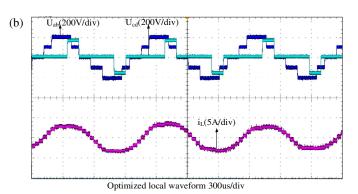

Light load (200 W), medium load (600 W), and heavy load (800 W) are shown in Figures 7–9. (a) The whole process of optimization, (b) the expansion diagram (as below). Online op-

timizations (taking sudden load reduction as an example) from medium to light load (600 W to 200 W), heavy to medium load (800 W to 600 W) respectively are shown in Figures 10 and 11.

FIGURE 7. Symmetrical light load offline optimization. (a) Optimize the whole process diagram. (b) Optimized local waveform.

FIGURE 8. Symmetrical medium load offline optimization. (a) Optimize the whole process diagram. (b) Optimized local waveform.

FIGURE 9. Offline optimization of symmetrical heavy load. (a) Optimize the whole process diagram. (b) Optimized local waveform.

FIGURE 10. Symmetrical online optimization of medium to light load. (a) Optimize the whole process diagram. (b) Optimized local waveform.

FIGURE 11. Symmetrical online optimization of heavy load to medium load. (a) Optimize the whole process diagram. (b) Optimized local waveform

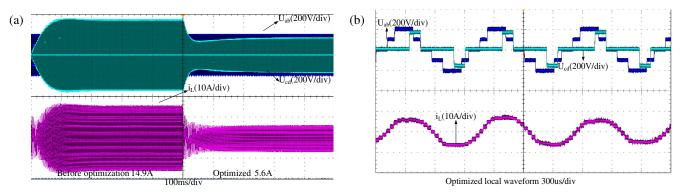

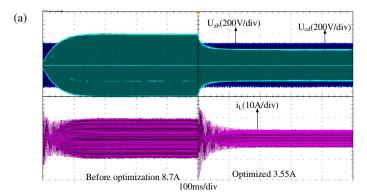

FIGURE 12. Asymmetrical offline optimization of light load. (a) Optimize the whole process diagram. (b) Optimized local waveform.

FIGURE 13. Asymmetrical offline optimization of medium load. (a) Optimize the whole process diagram. (b) Optimized local waveform.

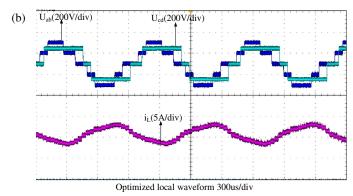

FIGURE 14. Asymmetrical offline optimization of heavy load. (a) Optimize the whole process diagram. (b) Optimized local waveform.

25

| Parameter                      | Value | Parameter                                    | Value |

|--------------------------------|-------|----------------------------------------------|-------|

| Number of HBSMs N              | 4     | Output capacitance $C_1/\text{mF}$           | 1.8   |

| DC-link $U_{dc}$ /V            | 200   | HBSM capacitance $C_O/\text{mF}$             | 1     |

| Inductance of arm $L_p/mH$     | 1     | Transmission inductance $L_s$ /mH            | 3.5   |

| Fundamental frequency $f/kHZ$  | 1     | Subside filtering capacitor $C_F/\mu F$      | 150   |

| Output resistance $R_0/\Omega$ | 10    | DC-side split capacitor $C_{DC}/\mathrm{mF}$ | 1     |

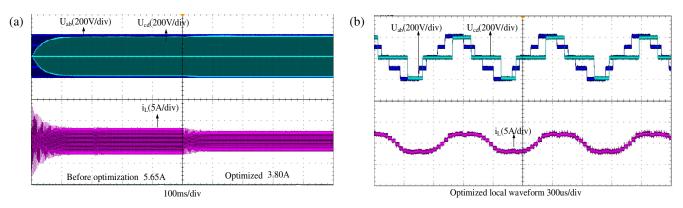

FIGURE 15. Asymmetrical online optimization of medium to light load. (a) Optimize the whole process diagram. (b) Optimized local waveform.

FIGURE 16. Asymmetrical online optimization of heavy to medium load. (a) Optimize the whole process diagram. (b) Optimized local waveform.

TABLE 3. Offline optimization of converter performance (Comparison with TPS.

| Modulations        | Current Optimized Ratio  | Voltage ripple ratio         | Transfer power ratio     |

|--------------------|--------------------------|------------------------------|--------------------------|

| Symmetric 5-Level  | L:15.64% M:9.83% H:6.55% | L:-14.44% M:-13.81%H:-9.97%  | L:+1.31%M:+1.36%H:+1.25% |

| Asymmetric 5-Level | L:17.35%M:11.23%H:6.98%  | L:-16.53% M:-14.79%H:-11.68% | L:+1.54% M:+2.13%H:1.64% |

**TABLE 4**. Online optimization of converter performance (Comparison with TPS, load shedding).

| Modulations        | <b>Current Optimized Ratio</b> | Voltage ripple ratio | Transfer power ratio |

|--------------------|--------------------------------|----------------------|----------------------|

| Symmetric 5-Level  | L:35.34% M:18.84%              | L:-15.24% M:-13.81%  | L: +2.61% M:+2.82%   |

| Asymmetric 5-Level | L:38.79% M:39.13%              | L:-19.33% M:-14.94%  | L:+2.34% M:+2.93%    |

#### 5.3. Optimization of Asymmetric Modulation

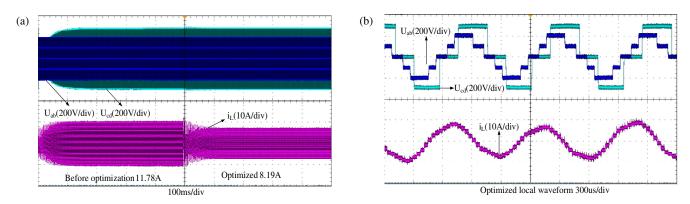

The offline optimization results of the asymmetric modulation under light load (200 W), medium load (600 W), and heavy load (800 W) respectively are shown in Figures 12-14.

The online optimizations (taking sudden load reduction as an example) from medium to light load ( $600\,\mathrm{W}$  to  $200\,\mathrm{W}$ ) and heavy to medium load ( $800\,\mathrm{W}$  to  $600\,\mathrm{W}$ ) respectively are shown in Figures 15 and 16.

#### 6. CONCLUSION

In this paper, we propose a load power classification prediction based on LSTM and an inductor current stress optimization algorithm based on secondary interpolation optimization. Experimental results show that asymmetric optimization is better than symmetric optimization, and online optimization results are better than offline optimization. As shown in Tables 3 and 4. L is for light load, M for medium load, and H for heavy load

As shown in the tables above, in terms of current stress and voltage ripple optimization, asymmetric optimization is better than symmetric optimization, but from the perspective of the transmission power ratio, the two effects are comparable.

# **REFERENCES**

- [1] Yun, J. and S. Cui, "Enhanced active thermal balancing strategy for three-phase dual-active bridge converter suppressing transformer flux saturation," *IEEE Transactions on Power Electronics*, Vol. 40, No. 4, 5014–5024, 2025.

- [2] Nitheesh, R., N. Lakshminarasamma, and B. A. Karuppaswamy, "Unison duty-phase peak current control for pole point inductorbased dual active bridge converter with zero DC bias current," *IEEE Access*, Vol. 13, 40 899–40 922, 2025.

- [3] Upputuri, R. P. and B. Subudhi, "A two-stage bidirectional DC-DC converter with a wide output voltage range for dc fast charging stations in E-mobility applications," *IEEE Journal of Emerging and Selected Topics in Power Electronics*, Vol. 13, No. 1, 294–303, Feb. 2025.

- [4] Ren, S., N. Song, J. Song, and N. Diao, "A phase-shifted full-bridge DC-DC converter with dual clamping circuits to eliminate voltage oscillation for electric vehicles charger," *IEEE Transactions on Transportation Electrification*, Vol. 11, No. 1, 3000–3014, Feb. 2025.

- [5] Li, L., M. Su, G. Xu, L. Jiang, and Y. Liu, "A soft-switched semi dual active half bridge converter with voltage match trapezoidal modulation control," *IEEE Transactions on Circuits and Systems* II: Express Briefs, Vol. 72, No. 1, 303–307, 2025.

- [6] Sha, J., J. Shen, H. Wang, G. Qiu, and Y. Sun, "Hybrid modulation-based discrete extended phase-shift control for dual active bridge DC-DC converter," *IEEE Transactions on Indus*trial Electronics, Vol. 71, No. 12, 15 633–15 642, Dec. 2024.

- [7] Goudarzitaemeh, S. and M. Pahlevani, "Extended phase shift control of a novel bidirectional DC–DC converter with direct power transfer," *IEEE Journal of Emerging and Selected Top*ics in Power Electronics, Vol. 12, No. 5, 4521–4537, Oct. 2024.

- [8] Liu, B., P. Davari, and F. Blaabjerg, "An optimized hybrid modulation scheme for reducing conduction losses in dual active bridge converters," *IEEE Journal of Emerging and Selected Top*ics in Power Electronics, Vol. 9, No. 1, 921–936, 2021.

- [9] Yan, Y., Q. Luo, T. Luo, J. Li, J. Xiong, and H. Xiao, "Current stress optimized strategy for the dual active bridge converter with triple-phase-shift and variable DC-link voltage control," *IEEE Transactions on Power Electronics*, Vol. 40, No. 6, 8344–8355, Jun. 2025.

- [10] Yang, P., M. Wang, S. Liu, S. Li, X. Chen, and Y. Peng, "Unilateral asymmetric triple phase shift modulation strategy for DAB converter compromising RMS current and soft-switching range," *IEEE Transactions on Circuits and Systems II: Express Briefs*, Vol. 71, No. 6, 3216–3220, Jun. 2024.

- [11] Pang, J., K. Wang, M. Wu, W. Zhou, Z. Zheng, and Y. Li, "Modulation and soft-switching optimization control of multilevel dual active bridge DC-DC converters," *IEEE Transactions* on *Power Electronics*, Vol. 40, No. 1, 1936–1951, 2025.

- [12] Song, C., N. Wang, A. Sangwongwanich, Y. Yang, and F. Blaabjerg, "Evaluation of capacitor voltage balancing control strategies for multilevel DAB converters," *IEEE Transactions on Power Electronics*, Vol. 39, No. 12, 15 548–15 564, Dec. 2024.

- [13] Ning, G., B. Dai, M. Su, L. Shu, and W. Xiong, "Interleaved buck-integrated modular multilevel DC transformer with wide voltage range for DC distribution grids," *IEEE Transactions on Power Electronics*, Vol. 39, No. 10, 12213–12223, Oct. 2024.

- [14] Jin, H., X. Li, W. Chen, B. He, S. Luo, and Y. Wang, "Modeling and current feedforward control of series-arm modular multilevel DC/DC converter with quasi-square-wave modulation," *IEEE Transactions on Power Electronics*, Vol. 40, No. 5, 6933–6950, May 2025.

- [15] Chaurasiya, S. and B. Singh, "A load adaptive hybrid DPS control for DAB to secure minimum current stress and full ZVS operation over wide load and voltage conversion ratio," *IEEE Transactions on Industry Applications*, Vol. 59, No. 2, 1901–1911, 2023.

- [16] Li, Z., Y. Pei, J. Liu, L. Wang, and Z. Leng, "Design and optimization of the MMC-based power electronic transformer considering ripple power transfer," *IEEE Transactions on Power Electronics*, Vol. 40, No. 4, 5352–5370, Apr. 2025.

- [17] Yang, P., M. Wang, L. Liu, S. Liu, X. Chen, Y. Peng, and J. Xu, "Optimal dual-side asymmetric modulation strategy for dual active bridge converter to improve efficiency over a wide voltage range," *IEEE Journal of Emerging and Selected Topics in Power Electronics*, Vol. 12, No. 2, 1596–1607, Apr. 2024.

- [18] Wang, Y., Y. Zhu, and H. Wen, "PSO-based current stress optimization for three-level dual active bridge DC-DC converters," in 2020 Chinese Automation Congress (CAC), 4283–4287, Shanghai, China, 2020.

- [19] Chaurasiya, S. and B. Singh, "A bidirectional fast EV charger for wide voltage range using three-level DAB based on current and voltage stress optimization," *IEEE Transactions on Transporta*tion Electrification, Vol. 9, No. 1, 1330–1340, 2023.

- [20] Song, C., A. Sangwongwanich, Y. Yang, Y. Pan, and F. Blaabjerg, "Analysis and optimal modulation for 2/3-level DAB converters to minimize current stress with five-level control," *IEEE Transactions on Power Electronics*, Vol. 38, No. 4, 4596–4612, 2023.

- [21] Zhou, S., I. Lashkov, H. Xu, G. Zhang, and Y. Yang, "Optimized long short-term memory network for LiDAR-based vehicle trajectory prediction through bayesian optimization," *IEEE Trans*actions on Intelligent Transportation Systems, Vol. 26, No. 3, 2988–3003, Mar. 2025.

- [22] Borah, J., M. S. M. Nadzir, M. G. Cayetano, H. Ghayvat, S. Majumdar, and G. Srivastava, "Timezone-aware auto-regressive long short-term memory model for multipollutant prediction," *IEEE Transactions on Systems, Man, and Cybernetics: Systems*, Vol. 55, No. 1, 344–352, Jan. 2025.

- [23] Emu, M., T. Rahman, S. Choudhury, and K. Salomaa, "Quantum long short-term memory-assisted optimization for efficient vehicle platooning in connected and autonomous systems," *IEEE Open Journal of the Computer Society*, Vol. 6, 119–128, 2024.

- [24] Li, W., C. Lin, S. Hosseininasab, L. Bauer, and S. Pischinger, "Lithium-ion battery SOH estimation based on a long short-term memory model using short history data," *IEEE Transactions on Power Electronics*, Vol. 40, No. 5, 7370–7384, May 2025.

- [25] Zewail, M. S. M., M. R. Elkadeem, M. M. M. Salama, D.-E. A. Mansour, and M. M. F. Darwish, "Quadratic interpolation optimization for planning of renewable energy-based DG units in power system networks," in 2024 25th International Middle East Power System Conference (MEPCON), 1–6, 2024.

- [26] Zhao, W., L. Wang, Z. Zhang, S. Mirjalili, N. Khodadadi, and Q. Ge, "Quadratic Interpolation Optimization (QIO): A new optimization algorithm based on generalized quadratic interpolation and its applications to real-world engineering problems," Computer Methods in Applied Mechanics and Engineering, Vol. 417, 116446, 2023.

- [27] Ekinci, S., D. Izci, V. Gider, L. Abualigah, M. Bajaj, and I. Zaitsev, "Efficient control strategy for electric furnace temperature regulation using quadratic interpolation optimization," *Scientific Reports*, Vol. 15, No. 1, 154, 2025.

- [28] Sun, Y., T. Yang, and Z. Liu, "A whale optimization algorithm based on quadratic interpolation for high-dimensional global optimization problems," *Applied Soft Computing*, Vol. 85, 105744, 2019.

- [29] Su, Y. and Y. M. Wu, "A fast iterative physical optics method with quadratic amplitude and phase integral terms," *IEEE Journal on Multiscale and Multiphysics Computational Techniques*, Vol. 9, 92–103, 2024.

- [30] Zhu, L., X. Cheng, X. Li, H. Tan, and H. Chen, "Research on calibration method for line-structured light sensor based on spatial

- quadratic surface fitting," *Measurement Science and Technology*, Vol. 36, No. 1, 015039, 2024.

- [31] Li, Y. and G. J. Kish, "The modular multilevel DC converter with inherent minimization of arm current stresses," *IEEE Transactions on Power Electronics*, Vol. 35, No. 12, 12 787–12 800, Dec. 2020.

- [32] Ansari, M. S., A. Shukla, and H. J. Bahirat, "A novel hybrid multilevel DC-DC converter employing trapezoidal modulation," *IEEE Transactions on Power Electronics*, Vol. 38, No. 10, 12 679–12 691, Oct. 2023.

- [33] Jin, H., W. Chen, and Y. Wang, "A series-arm modular multilevel DC/DC converter with variable duty cycle quasi-squarewave modulation for ZVS operation," *IEEE Transactions on Power Electronics*, Vol. 39, No. 10, 12 185–12 199, Oct. 2024.

- [34] Lin, F., X. Zhang, X. Li, C. Sun, G. Zsurzsan, W. Cai, and C. Wang, "Ai-based design with data trimming for hybrid phase shift modulation for minimum-current-stress dual active bridge converter," *IEEE Journal of Emerging and Selected Topics in Power Electronics*, Vol. 12, No. 2, 2268–2280, Apr. 2024.

- [35] Wang, N., Y. Wang, W. Hu, J. Chen, Z. Li, and Z. Chen, "A PSO-ANN-aided DC-bias current suppression strategy for three-phase DAB converter with variable duty cycles," *IEEE Transactions on Industrial Electronics*, Vol. 72, No. 2, 1586–1596, Feb. 2025.